新着情報

OB/OG会

2025/8/23(土)にOB/OG会を開催します! MLで連絡していますが、受け取れていない方は連絡ください!

「時分割MIMO」による高速ミリ波通信に成功

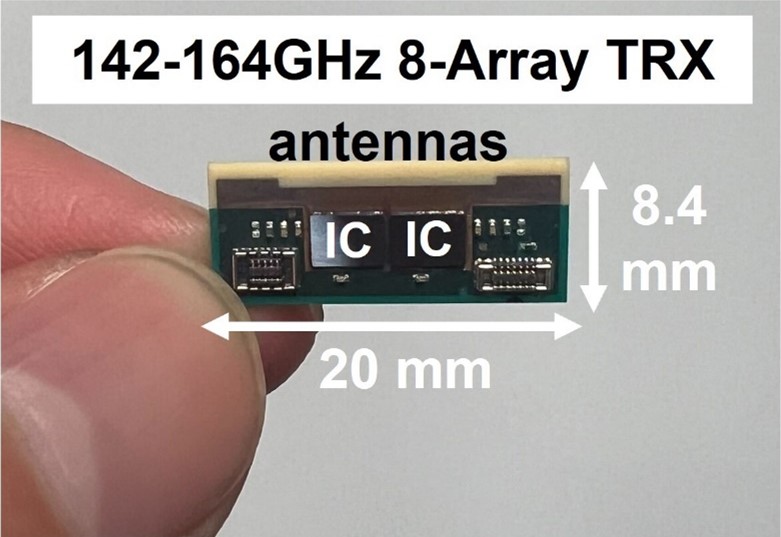

published on150 GHz帯超小型・低消費電力アンテナ一体無線機モジュールを開発

published onVLSI Symposiumで発表

VLSI Symposiumで発表しました。下記はデモの様子。

お花見

Wang Chunさん、手島精一記念研究賞(留学生研究賞)受賞

博士研究員のWang Chunさんが、手島精一記念研究賞(留学生研究賞)を受賞しました。おめでとうございます!

ISSCC 2025

Eveninig Panel: “Future of Analog Design: Still Magical or Mostly Digital?”

Forum: Wireless Communication Technology for Space Applications: From Satellite to Dish and Smartphones

Kenichi Okada, Institute of Science Tokyo, Tokyo, Japan

“Foldable Phased-Array Transceivers for Satellite Communications”

Xu Dingxinさんが、IEEE SSCS Predoctoral Achievement Award受賞

Xu Dingxinさんが、IEEE SSCS Predoctoral Achievement Awardを受賞しました!

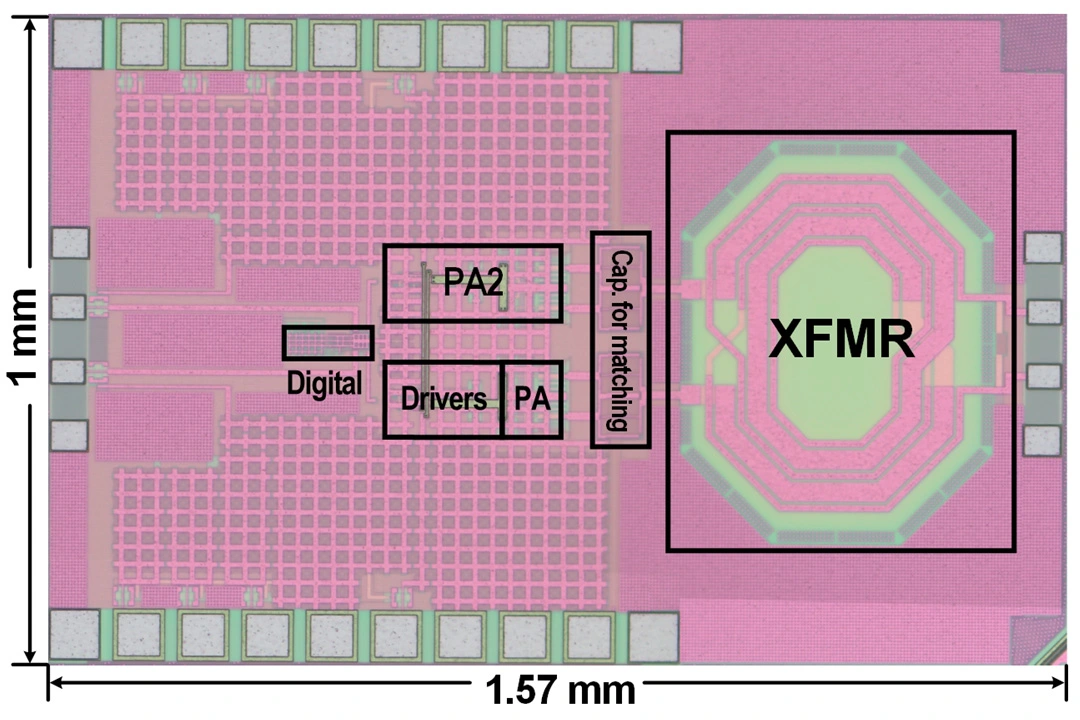

Beyond 5Gに向けた新型デジタル送信機CMOS ICを開発

ISSCC 2025で6件発表

ISSCC 2025で発表します!

Forum Presentation

- Kenichi Okada, “Foldable Phased-Array Transceivers for Satellite Communications”

Regular Session

- Yuncheng Zhang, et al.,“A Power-Efficient CORDIC-less Digital Polar Transmitter Using 1b DSM-Based PA Supporting 256-QAM”

- Sena Kato, et al.,“A 256-Element Ka-Band CMOS Phased-Array Receiver Using Switch-Type Quadrature-Hybrid-First Architecture for Small Satellite Constellations” (白根研)

山崎雄大さん、Minzhe Tangさん、Daxu Zhangさんが、Student Research Previewで発表します。

益先生 最終講義 2025/3/8

益先生の最終講義、2025/3/8です! 是非、ご参加ください!

●益 一哉先生 最終講義とお祝いの会のご案内

https://x.gd/UnSnO (聴講も申し込みが必要です)

〇最終講義 「未来を先送りしない」

日時:2025年3月8日(土) 14時~16時 (受付開始:13時)

場所:東京科学大学 大岡山キャンパス 蔵前会館

方法:ハイブリッド開催(オンサイト+zoom配信)

登録:https://forms.gle/3nkAVDsJ8oCcrmCRA (2月3日まで)

〇懇親会

日時:2025年3月8日(土) 18時~20時 (17時30分 開場)

場所:新横浜プリンスホテル 5階 シンフォニア

申込 https://forms.gle/s4X1tTcJeWBWcpXX7 (2月3日まで)

●連絡先 masulecture@nasu.iir.titech.ac.jp

最終講義 「「未来を先送りしない」 益 一哉

私は、1982年から半導体集積回路の研究を大学で行い、2024年9月まで東工大学長を務め、現在産総研に勤務しております。本講演では、研究者・教育者としての取り組み、学長として取り組んだこと、そしてこらからについてお話させていただきます。

東北大において研究者として歩み始めた当初から、産学連携による研究推進は当たり前のように行いました。1980年代90年代、日本の半導体に勢いのあった時は、何をやっても楽しい時期でした。東工大に戻り、2000年から2018年まで、高速・高周波CMOS集積回路設計やCMOSーMEMS集積回路研究に多くの学生や産業界の方と取り組みました。一定の成果は出せたのかもしれませんが、日本の半導体産業は衰退してしまいました。

Prof. Hua Wang

ETH(スイス連邦工科大学チューリッヒ校)のHua Wang教授に講演いただきました。

Speaker: Prof. Hua Wang (ETH, Zurich, Swiss)

Title: “Fundamentals of RF and mm-Wave Power Amplifier Designs”

Abstract: This talk presents a focused overview of mm-wave power-amplifier (PA) designs in silicon, including design fundamentals, advanced PA architectures, and state-of-the-art design examples. As phased arrays and MIMO systems have become ubiquitous in various wireless communication and sensing applications, they pose a completely new level of system complexity and different and often tighter requirements on the wireless frontend electronics, in particular the PAs. The talk will start with an introduction of PA performance metrics and their impacts on wireless systems. Next, it presents the design fundamentals of PA active devices and passive networks as well as power combining strategies. The tutorial discusses advanced PA architectures, including Doherty, Outphasing, LMBA, and Coupler-Balun Doherty PAs, for high efficiency, linearity, and bandwidth. Further, advance and challenges of high mm-Wave PAs in large-scaled arrays will be covered to address various emerging wireless applications. Finally, the talk will conclude with several state-of-the-art mm-wave PA design examples.

Top Contributors of A-SSCC 2005-2023受賞

松澤先生と岡田先生が、国際会議A-SSCCの2005-2023まで期間におけるTop Contributorに選出されました。

EuMWでDバンド無線機のデモ

EuMW (European Microwave Week)で、Dバンド無線機のデモを行いました!!

OB

NVIDIAで働いているOBが研究室に遊びに来てくれました!!

OB/OG Party

5年ぶりにOB/OG会を開催しました!

OB/OG MLが届いていない人は secretaryssc.pe.titech.ac.jp まで連絡ください!

Prof. Patrick Mercier

カリフォルニア大学サンディエゴ校(UCSD)からのPatrick Mercier教授に東工大に訪問頂き、ご講演くださいました!

Speaker: Prof. Patrick P. Mercier, University of California, San Diego (UCSD)

Title: “Low-Power Standards-Compatible Wireless Communications Circuits for Next-Generation IoT and Wearable Applications”

Abstract:

Emerging Internet-of-Things (IoT) devices for use in smart homes, wearable systems, industrial monitoring, smart cities, and beyond all require robust yet low-power wireless communications. Unfortunately, most current wireless standards do not intrinsically support low-power operation due to strict requirements on modulation formats, data rates, linearity, packet overheads, and so on. These restrictions impose minimum power consumption requirements for cellular standards (e.g., GSM, LTE, and 5G) and WiFi, but also surprisingly limit the ability of supposedly low-power standards (e.g., Bluetooth Low Energy and Narrowband-IoT) from reaching new application-enabling power levels.

This presentation will outline the major challenges facing power reduction in modern wireless systems, and will describe several possible solutions to these challenges. Specifically, we will explore the use of wake-up receivers as a means to reduce the power overhead of between-node synchronization. Then, we will discuss an alternative communication scheme that can help to reduce the power of communication in WiFi, BLE, and body-area-network systems by >1,000x through use of standards-compatible backscatter communication systems, including the latest developments incorporating retroreflection and beam steering. We will also discuss related sensing circuit opportunities to round out the application space.

Hansさんの博士論文発表会

博士課程のHans HERDIANさんの博士論文発表会を開催しました!

VLSI Symposiumで3件発表

IEEE Symposium on VLSI Technology & CircuitsでChenxin Liuさん、加藤さん、Yi Zhangさんが発表しました!

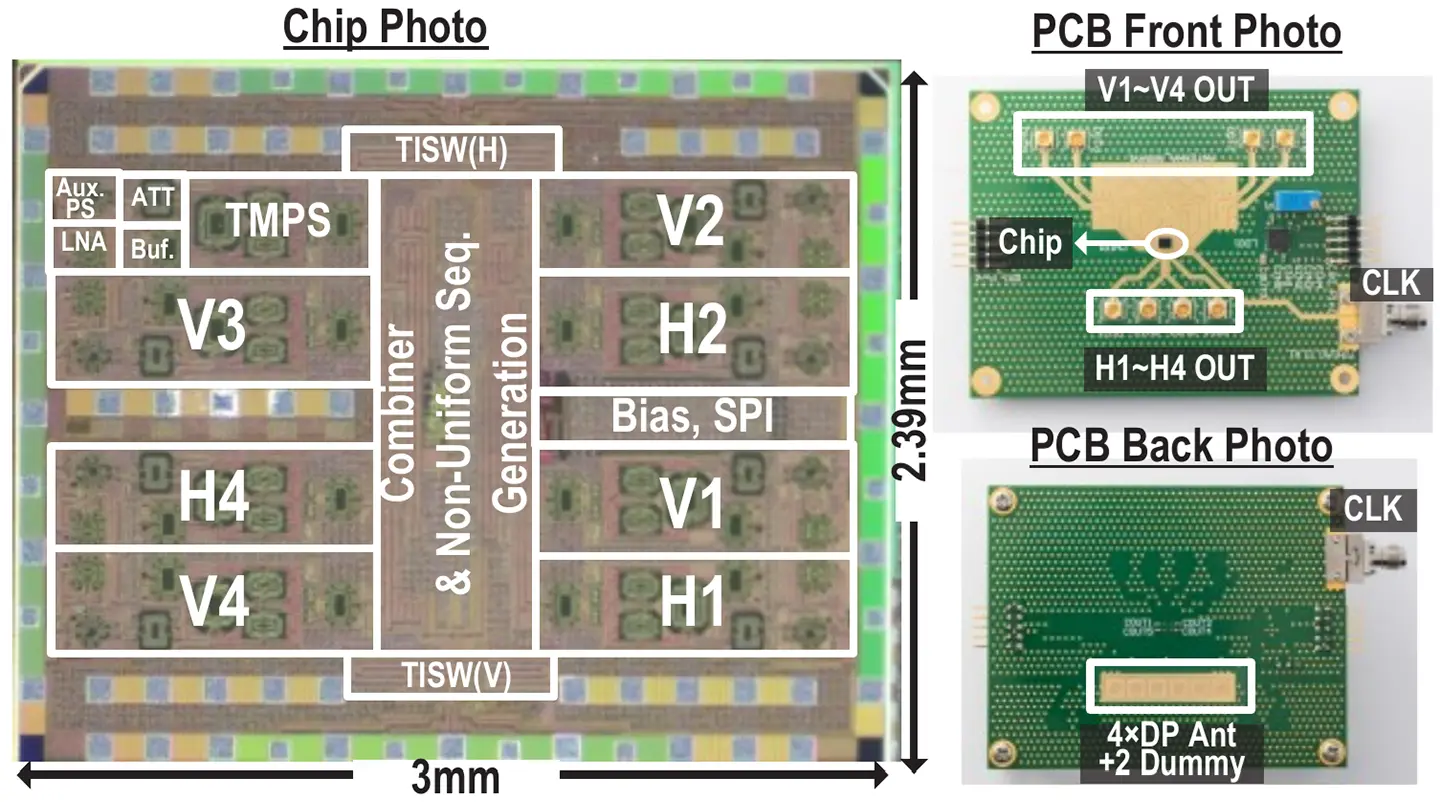

- Chenxin Liu “A 640-Gb/s 4x4-MIMO D-Band CMOS Transceiver Chipset”

- Sena Kato “A 28GHz 5G NR Wirelessly Powered Relay Transceiver Using Rectifier-Type 4th-Order Sub-Harmonic Mixer”

- Yi Zhang “A 28GHz 4-Stream Time-Division MIMO Phased-Array Receiver Utilizing Nyquist-Rate Fast Beam Switching for 5G and Beyond”

サブテラヘルツ帯CMOS ICで640Gbpsの無線伝送に成功

超高速無線通信を用いた遠隔医療や自動運転の実装に前進