Latest News

Cherry Blossom Viewing at Okada Lab

The rain stopped, and although it was a bit cold, we had a great time.

Two Members from Our Lab Selected as Representatives at the Commencement Ceremony

At the commencement ceremony of Institute of Science Tokyo, two members from our laboratory were selected as representatives.

Yudai Yamazaki was chosen as the representative of doctoral graduates in the Electrical and Electronic Engineering Course, and Kotaro Ito was selected as the representative of undergraduate students in the Department of Electrical and Electronic Engineering.

Congratulations on their graduation!

Yudai Yamazaki’s JSSC paper on developing an ultra-compact phased-array transceiver for 6G applications has been published.

A JSSC paper by Yudai Yamazaki on developing an ultra-compact phased-array transceiver for 6G applications has been published.

This paper is related to the research result announced on June 13, 2025, “Development of an Ultra-Compact, Low-Power Antenna-Integrated Radio Module in the 150 GHz Band.”

Reference URLs:

Yudai Yamazaki received the Student Research Preview Poster Award at ISSCC 2026, held in San Francisco in February 2026.

At ISSCC 2026, Yudai Yamazaki received the Poster Award for his presentation in the Student Research Preview (SRP). Congratulations!

Poster Title: A High-Power-Density D-Band Phased-Array Transceiver in 65nm CMOS for 6G UE Module

Announcement: Graduate School Information Sessions School of Engineering, Department of Electrical and Electronic Engineering (Ookayama & Suzukakedai)

The Department of Electrical and Electronic Engineering will hold graduate school information sessions for those considering admission or further study in the field. The sessions will mainly provide information on the master’s program and introduce our laboratories. Both sessions will be held in a hybrid format (on-site + Zoom).

For details on application procedures, admission requirements, and the official guidelines, please also refer to the University’s admissions webpage:

■Event Date and Time

Session 1 (Ookayama) Friday, March 27, 2026, 13:00–17:00

Session 2 (Suzukakedai) Friday, May 15, 2026, 13:00–17:00

■Program

13:00–14:00 Graduate Admissions Information Session (Electrical and Electronic Engineering)

14:00–17:00 Laboratory Tours

■Venue

Session 1 (Ookayama)

Ookayama Campus, South Building 2, Lecture Room S2-204 (S221) / Hybrid (Zoom)

Session 2 (Suzukakedai)

Suzukakedai Campus, Building J2, Lecture Room J2-203 (tentative) / Hybrid (Zoom)

■Who Should Attend

Undergraduate and graduate students who plan to apply to graduate school

Those considering admission to the School of Engineering, Department of Electrical and Electronic Engineering

Those wishing to enroll in September 2026 or April 2027

■Capacity

On-site: 150 participants

Online: No limit

■Language

Japanese

■Registration

Please register in advance via the form below.

Session 1 (Ookayama): Application Form

Session 2 (Suzukakedai): Application Form

■Registration Deadline

Registration is open until shortly before each session.

Miniaturized radar on a chip for next-generation wireless networks

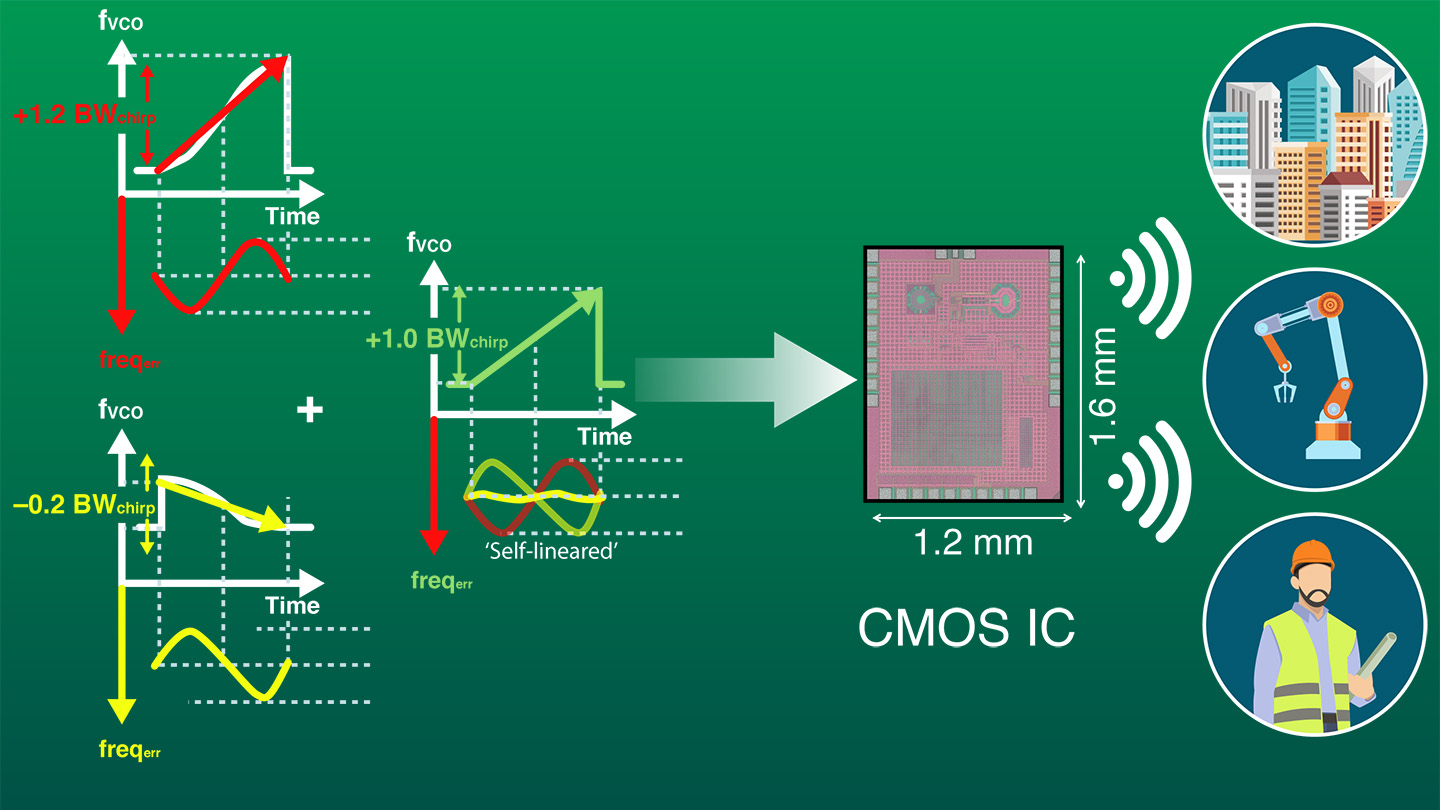

A miniaturized radar chip, developed by researchers at Science Tokyo, advances Integrated Sensing and Communication for Beyond 5G and 6G systems. Measuring just 0.24 mm2 and consuming only 9.8 mW, the compact, low-power device generates high-speed, highly linear chirps by embedding linearization directly into the hardware, overcoming traditional speed-versus-accuracy limits and enabling precise sensing for edge and Internet-of-Things devices.

Prof. Hua Wang

Speaker: Prof. Hua Wang (ETH, Zurich, Swiss)

Title: AI-Assisted for Radio-Frequency Integrated Circuits at ETH Zurich

Abstract: In recent years, as AI for Science is gaining increasing momentum, there are rapidly growing interest in applying AI tools to facilitate RFIC designs or explore new design spaces. In this seminar talk, I will present a few on-going AI4RF projects at my IDEAS group at ETH Zurich. We will start with our project of AI-assisted template-seeded pixelated design for multi-metal-layer EM structures, which explores a new approach for efficient exploration and exploitation of the design space. Next, we will introduce our transfer learning assisted fast design migration, which potentially enables efficient design migrations over technology nodes and operating frequencies. Finally, we will present out project on top-metal-only RFIC redesigns for fast specs-to-silicon iteration enabled by AI-assisted inverse design. Finally, we will discuss challenges and future directions.

Prof. Mehdi Saligane

Speaker: Prof. Mehdi Saligane (Brown University, USA)

Title: AI for Chips & Chips for AI

Abstract: The exploding scale of modern applications is stretching yesterday’s integrated-circuit (IC) design flows beyond their limits. This talk presents a unified, open, and highly-automated paradigm—AI for Chips & Chips for AI—that simultaneously (i) harnesses artificial intelligence in EDA to build better silicon and (ii) architects silicon that runs AI better.

AI for Chips - Traditional analog layout still relies on expert heuristics. We introduce Agentic-RL gLayout, a goal-conditioned reinforcement-learning agent that replaces hand-tuned placement and routing with policy-driven planning, action, and self-correction. The agent ingests high-level objectives, observes the evolving layout state, and chooses between primitive commands and high-level macros. Positive rewards track goal attainment; penalties capture DRC violations, area bloat, and parasitics, producing cleaner, compact, and rule-compliant layouts without manual intervention. Built atop open-source engines such as OpenROAD, Open Se Cura, and OpenFASoC, the framework pushes layout quality while democratizing access to sophisticated analog design automation. Chips for AI - Conversely, deploying large language model (LLM) workloads at the edge demands silicon tuned for extreme efficiency. We unveil a hardware–software co-design stack centered on ConSmax, a highly parallel, element-wise alternative to Softmax that slashes latency and energy. By co-optimizing network topology, arithmetic precision, and accelerator micro-architecture, the framework meets sub-millisecond deadlines, preserves privacy, and cuts cloud dependence.

Finally, this talk will walk through an open chip design infrastructure augmented with LLM-guided code, circuit, and layout generation that turns hardware creation into a rapid feedback loop, where AI sharpens the EDA tools, while tailored accelerators speed up AI. Closing the “AI-for-chips, chips-for-AI” cycle should make taping-out test chips possible in weeks instead of years, thus propelling the next wave of semiconductor innovation.

Bio: Mehdi Saligane received the B.S. and M.S. degrees in Electrical Engineering Systems and Industrial Computing from École Polytechnique de Grenoble in 2009, and the M.S. Degree in electrical engineering from the University of Grenoble in 2011, and the Ph.D. degree in Electrical Engineering and Computer Science from the University of Aix-Marseille (IM2NP), France, in 2016. From 2010 to 2015, he was part of the Central Research and Development Group at STMicroelectronics in Crolles, France, focusing on adaptive, ultra-low-power digital design. In 2015, he joined the Michigan Integrated Circuit Laboratory at the University of Michigan, Ann Arbor, MI, USA, as a visiting research investigator. In 2019, he served as a Visiting Researcher at the University of California, San Diego, San Diego, CA, USA. He is a founding member of both the OpenROAD and OpenFASOC Projects. Since 2020, he has been a Research Faculty member at the University of Michigan. In 2024, he joined Google Research as a Visiting Faculty Member, and in 2025, he joined Brown University as an Assistant Professor of Electrical and Computer Engineering. His research interests include secure low-power and energy-efficient IC design, Biosensors, analog/mixed-signal design automation and open-source EDA, and custom architectures for lightweight language model accelerators. Dr. Saligane is the recipient of the 2023 Google Cloud Research Innovators Award and the 2021 Google Research Faculty Award. He served in leadership roles at the CHIPS Alliance from 2020 to 2023, including as Chair of the Analog Working Group and as a member of the Technical Steering Committee. Since 2020, he has served on the IEEE Solid-State Circuits Society (SSCS) Open-Source Ecosystem (TC-OSE) Technical Committee and has been the Chair since 2025. In addition, he co-founded and organizes the SSCS Chipathon Design Contest and the SSCS Code-a-Chip Notebook Competition at ISSCC and VLSI Symposium, fostering student engagement with open-source chip design.

ISSCC 2026, 4 presentations

Presentations in ISSCC 2026

Forum Presentation

- Kenichi Okada, “Exploration of 6G FR3 for Coverage, Capacity, and Sensing in Edge AI Era”

Regular Session

- Daxu Zhang, et al., “A 9.7GHz Self-Linearized-VCO-Based FMCW Chirp Generator Achieving 1.56GHz/µs Slope and 0.57µs Duration with 0.094% rms Frequency Error”

Dongfan Xu, Minghao Fan will present their work in Student Research Preview.

Prof. Jeffrey S. Walling

Seminar

Speaker: Prof. Jeffrey S. Walling (Virginia Tech, USA)

Title: Bits-to-Waves: Digital RF, mm-Wave and THz Systems to Enable the Next-G

Abstract: Mixer-based transmitters have been dominant for approximately 100 years. However, for more than a decade RF-DACs have demonstrated the ability to combine the functionality of the DAC, upconverter and amplification stages of a transmitter into a single block. The switched-capacitor power amplifier (SCPA) is a versatile RF-DAC that operates in a voltage mode and uses transistors only as switches. This talk provides a tutorial introduction of the SCPA and presents architectural examples that enable both frequency reconfigurability and operation up to mm-Wave, supporting up to 3Gb/s transmission rates. New uses of algorithmic designs for RF passives will also be introduced.

Speaker Bio: Jeff Walling received his BS from University of South Florida and his MS and PhD from University of Washington, all in Electrical Engineering. He has held industrial positions at Motorola, Intel, Qualcomm and Skyworks. His research has primarily focused on circuits for wireless communications and sensing. From 2012 to 2019, he was an assistant, then associate professor at University of Utah. Then he was head of RF transceivers at Tyndall National Institute in Cork, Ireland. Since 2021, he is an associate professor at Virginia Tech. He has served as an associate editor for TCAS-II, TCAS-I and JSSC, and on the technical program committees of the IEEE RFIC, ISSCC and NEWCAS conferences. He is a senior member of the IEEE and has more than 80 papers in peer reviewed conferences and journals.

A-SSCC 2025

Two students presented their work in IEEE Asian Solid-State Circuits Conference (A-SSCC), Daejeon, Korea.

Dongfan Xu, Minzhe Tang, Haiyun Gu, Ziyuan Ren, Yilun Chen, Minghao Fan, Yuxuan Liu, Daxu Zhang, Yi Zhang, Zheng Li, Yuncheng Zhang, and Kenichi Okada,

“A Ka-Band Time-Modulated Variable Gain Amplifier with 30-dB Gain Tuning and <2° Phase Variation via Duty Cycle Control”

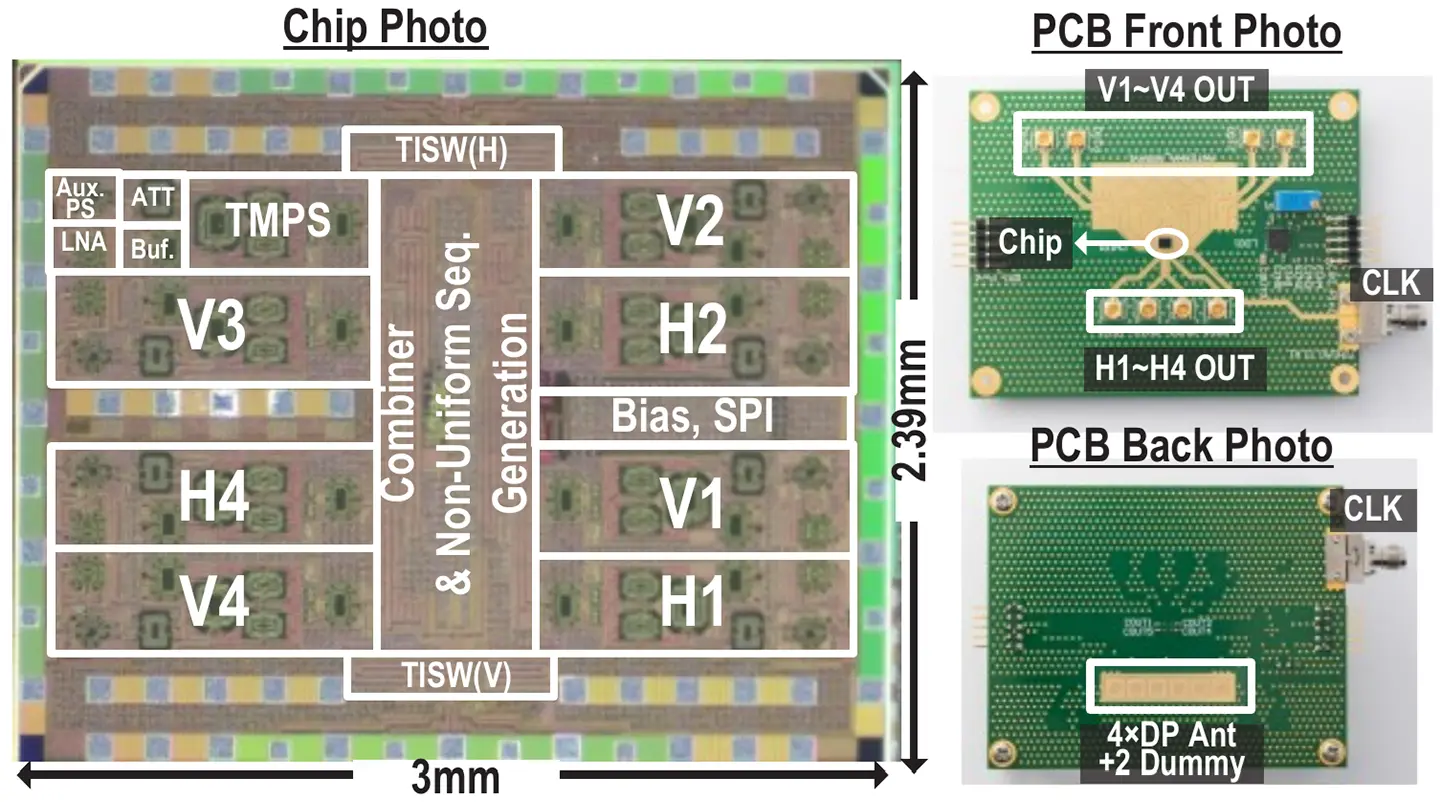

Sunghwan Park, Yudai Yamazaki, Carrel de Gomez, Chenxin Liu, Jun Sakamaki, Hiroyuki Sakai, Kazuaki Kunihiro, and Kenichi Okada,

“A High-Efficient 154GHz 4TX/4RX FMCW Radar Chipset in 65nm CMOS”

Kenichi Okada“How to cultivate good chip designers” Panel discussion

“Millimeter-Wave Circuit Innovations for 6G and Beyond”

KAIST EE Global Symposium

IEEE/IEIE ICCE Asia“Millimeter-Wave Circuit Innovations for 6G and Beyond”

also presented at Seoul National Univerisity

Submission completed!

A picture after paper submission!

2025 OB/OG Party

We held an OB/OG reunion on Aug. 23th, 2025

If you haven’t received emails from the OB/OG mailing list, please contact us at secretary@ssc.p.isct.ac.jp.

Mr. Yudai Yamazaki has won the Best Poster Presentation Award at the MCRG Symposium!

At the 2nd MCRG (Mobile Communication Research Group) Symposium of 2025, Mr. Yudai Yamazaki was recognized as the researcher who delivered the most outstanding poster presentation. Congratulations!

**Poster Title: “**A 150GHz Compact Phased-Array Transceiver for 6G UE"

Prof. Chung-Tse Michael Wu

Prof. Chung-Tse Michael Wu (National Taiwan University) visited our lab!

Prof. Yu-Hsiang Cheng

Prof. Yu-Hsiang Cheng (National Taiwan University) visited our lab!

Prof. Mark Rodwell

Prof. Mark Rodwell (UCSB) visited our university at July 15th, 2025! Welcome!!!

Lecturer: Prof. Mark Rodwell(University of California, Santa Barbara)

Title: 100-300 GHz Wireless: transistors, ICs, systems

Date & Time: Tuesday, July 15, 2025, 15:45 – 17:30

Abstract: We describe the opportunities, and the research challenges, presented in the development of 100-300GHz wireless communications and imaging systems. In such links, short wavelengths permit massive spatial multiplexing both for network nodes and point-point links, permitting aggregate transmission capacities approaching 1Tb/s. 100-300GHz radar imaging systems can provide thousands of image pixels and sub-degree angular resolution from small apertures, supporting foul-weather driving and aviation. Challenges include the mm-wave IC designs, the physical design of the front-end modules, the complexity of the back-end digital beamformer required for spatial multiplexing, and, for imaging, the development of system architectures requiring far fewer RF channels than the number of image pixels. We will describe transistor development, IC design, and system design, and describe our efforts to develop 140GHz massive MIMO wireless hubs, and 210GHz and 280GHz MIMO backhaul links.

Mr. Yudai Yamazaki has received the Minister of Education, Culture, Sports, Science and Technology Award at the 38th Advanced Technology Award for Pioneering Creativity.

Mr. Yudai Yamazaki received the highest honor in the student category: the Minister of Education, Culture, Sports, Science and Technology Award.

OB/OG Gathering

We will hold an OB/OG gathering on Saturday, August 23, 2025! We have sent out the information via the mailing list, but if you haven’t received it, please contact us!