Latest News

Prof. Wei Deng and Prof. Xiang Gao

Prof. Wei Deng (SSCS DL, Tsinghua University) and Prof. Xiang Gao (Zhejiang University) visited Tokyo Tech!

5/2(Thu) 15:30-16:30 Prof. Wei Deng (SSCS DL)

“Joint Radar-communication CMOS Transceiver”

16:30-17:30 Prof. Xiang Gao

“Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation”

★Details of each talk

(Talk 1) Speaker: Prof. Wei Deng (Tsinghua University)

Title: Joint Radar-communication CMOS Transceiver: From System Architecture to Circuit Design

Abstract: Recent years, millimeter-wave and Terahertz radar systems for sensing and radio systems for communication have attracted substantial attention both from the academia and industry. In addition, there is an increasing demanding for fusing both the hardware platform and frequency band of the radar and radio system, which has advantages of energy efficiency, performance optimization, spectrum sharing/efficiency, compact size, interference management, and the overall cost, as compared to assembling of two distinct systems. This lecture will introduce the current and future trends in the emerging joint radar-communication CMOS transceiver from system architecture to circuit design.

Bio: Wei Deng received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Japan, in 2013. He was with Apple Inc., Cupertino, CA, USA, working on RF, mm-wave, and mixed-signal IC design for wireless transceivers and Apple A-series processors. Currently he is with Tsinghua University, Beijing, China, as an Associate Professor. His research interests include RF, mm-wave, terahertz, and mixed-signal integrated circuits and systems for wireless communications, sensing, and imaging systems. He has authored or co-authored more than 160 IEEE journal and conference articles. Dr. Deng is a TPC Member of ISSCC, VLSI, A-SSCC, CICC and ESSCIRC. He has been an Associate Editor and a Guest Editor of the IEEE Solid-State Circuits Letters (SSC-L), a Guest Editor of the IEEE Journal of Solid-state Circuits (JSSC), and a Distinguished Lecturer of the IEEE Solid-State Circuits Society (SSCS).

(Talk 2) Speaker: Prof. Xiang Gao (Zhejiang University)

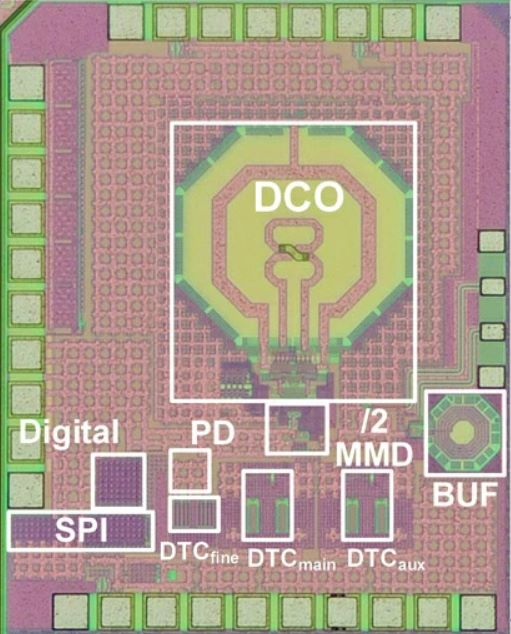

Title: Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation

Abstract: Conventional PLLs detecting phase error in the time domain using a phase frequency detector often suffer from poor in-band phase noise due to the limited phase detector (PD) gain. The (Sub-)Sampling PLL is becoming a popular low jitter PLL architecture due to high gain of the SSPD. However, the high gain SSPD has a limited linear detection range, which is a challenge in fractional-N operation with the quantization noise. This talk presents a SPLL design with a merged constant-slope digital-to-time converter(DTC) and sampling phase detector (CSDTC-SPD). It realizes phase detection as well as quantization noise cancellation in a single ramp generation.

Bio: Xiang Gao received the B.E. degree from the Zhejiang University, Hangzhou, China, in 2004 and the M.Sc. and Ph.D. (cum laude) degrees from the University of Twente, Enschede, The Netherlands, in 2006 and 2010 respectively, both in electrical engineering. From 2010 to 2016, he was a principal engineer and design manager with Marvell Semiconductor, Santa Clara, CA, focusing on analog and RF IC design for wireless transceivers. From 2016 to 2018, he was an Engineering Director with Credo Semiconductor, Milpitas, CA, working on high-speed SerDes. Since August 2018, he has been a Faculty member at Institute of VLSI Design, Zhejiang University, China. He is an IEEE senior member, and TPC member of RFIC(2014-current)、CICC(2016-2023) and ISSCC(2015-2019, 2024-current).

Chun Wang's thesis presentation

Chun Wang’s thesis presentation!

Cherry Blossom Party

Ohanami Party (Cherry Blossom Party)!

Prof. Vadim Issakov

On March 28, the IEEE MTT-S Japan/Kansai/Nagoya Chapter hosted the DML Lecture (Distinguished Microwave Lecture), in which Prof. Vadim Issakov of the Technische Universität Braunschweig (TU-Braunschweig) gave a lecture on his millimeter-wave radar research.

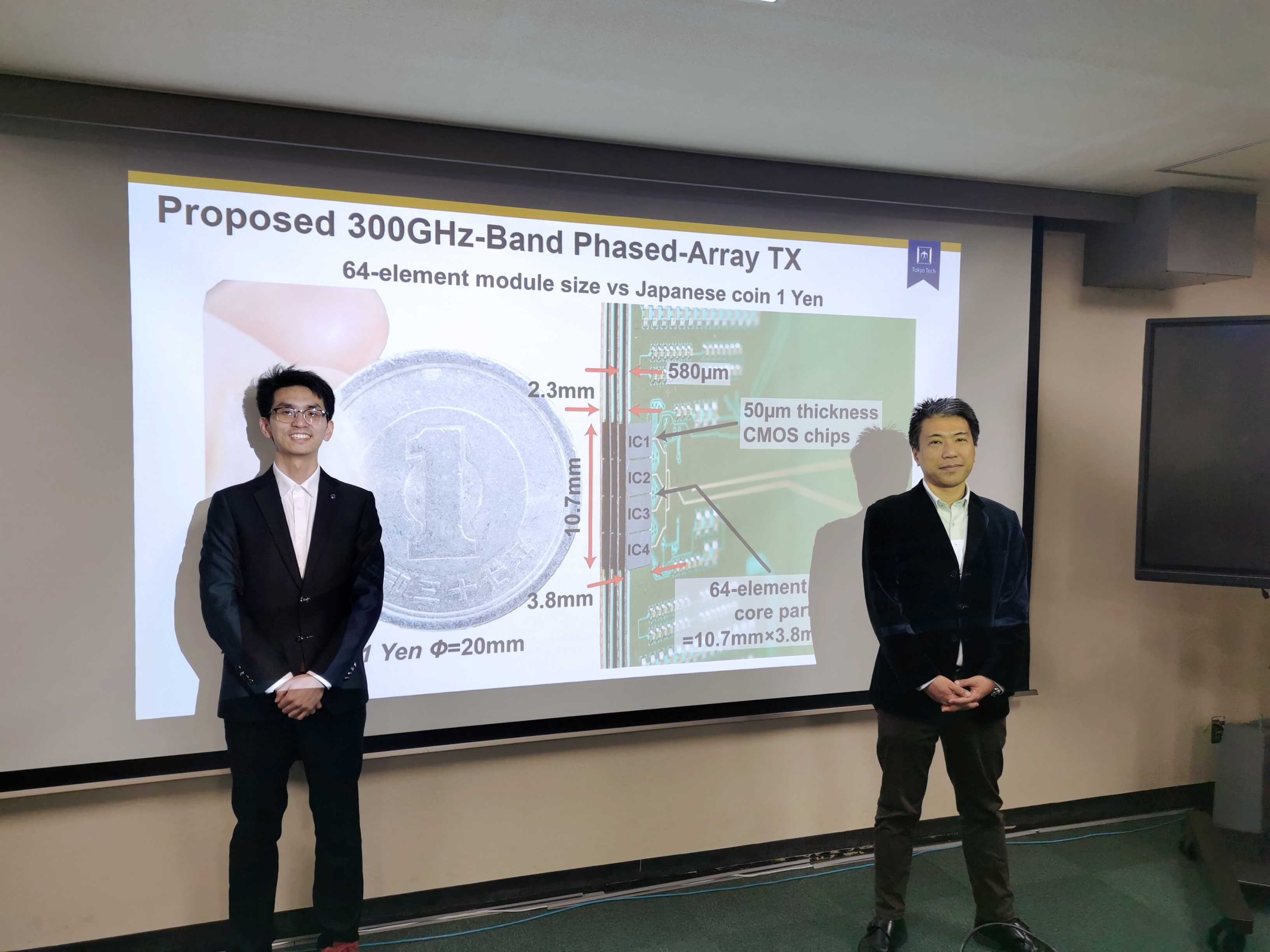

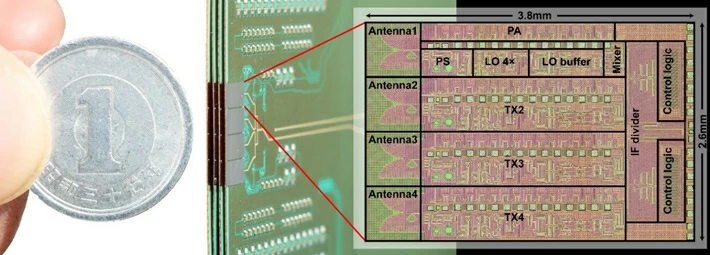

Tapping into the 300 GHz Band with an Innovative CMOS Transmitter

published onCombating Fractional Spurs in Phase Locked Loops to Improve Wireless System Performance in Beyond 5G

published onISSCC Student Research Preview (SRP) Poster Award

Dingxin Xu won ISSCC 2023 Student Research Preview (SRP) Poster Award!

ISSCC 2024, 6 presentations

Presentation in ISSCC 2024.

Regular Session

- Dingxin Xu, et al.,“A 7GHz Digital PLL with Cascaded Fractional Divider and Pseudo-Differential DTC Achieving -62.1dBc Fractional Spur and 143.7fs Integrated Jitter”

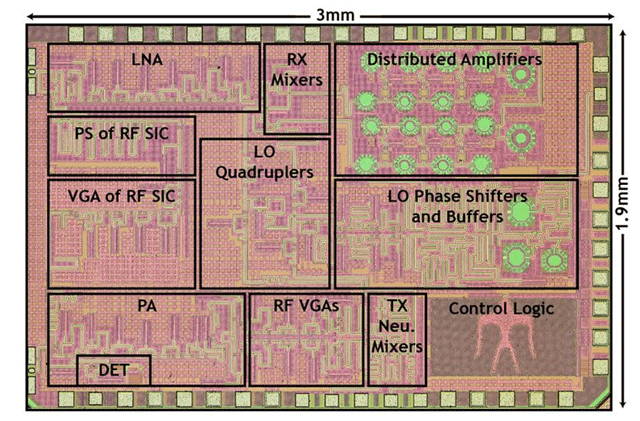

- Chun Wang, et al.,“A 236-266GHz 4-Element Amplifier-Last Phased-Array Transmitter in 65nm CMOS”

Forum Presentation

- Kenichi Okada, “Low-Power Fractional-N Digital PLL Design Techniques”

Keito Yuasa, Yi Zhang, and Chenxin Liu will present their work in Student Research Preview.

Prof. Vadim Issakov

Prof. Dr. Vadim Issakov (Technische Universität Braunschweig) came to our lab at Nov. 21st, 2023!

Celebration Party for Prof. Matsuzawa's Donald O. Pederson Award, and Prof. Okada's IEEE Fellow

We had a celebration party for Prof. Matsuzawa and Prof. Okada, and more than 90 alumni and guests attended the party.

Prof. Masu (Tokyo Tech President)

Prof. Dosho (First-graduated doctor)

Prof. Miyahara (past Assistant Professor)

Prof. Motomura

Prof. Ikeda (guest from University of Tokyo)

Mr. Yamazaki (doctoral student)

Party

Congratulations!!

Chun Wang-san and Dinxin Xu-san!!

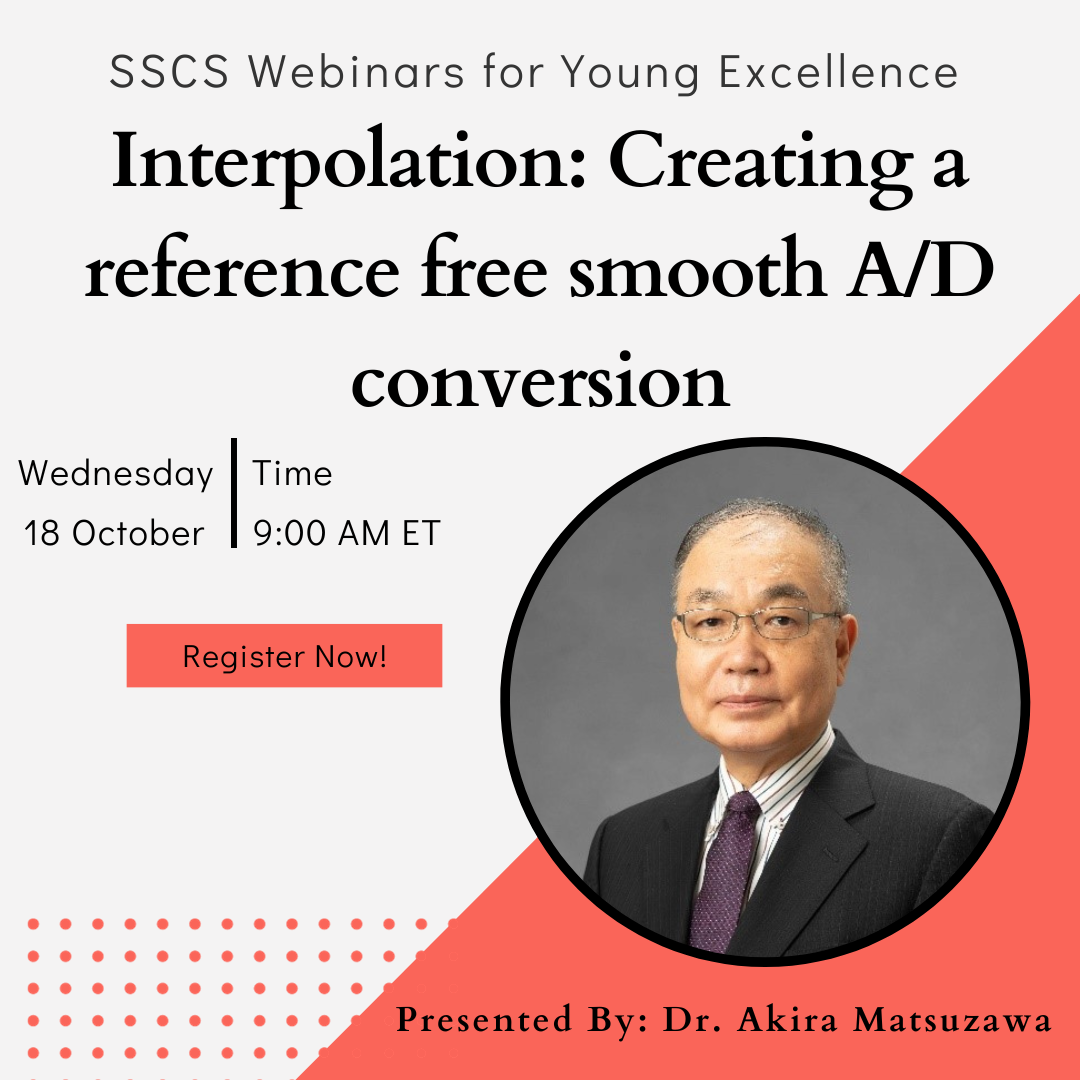

Webinars for Young Excellence: Interpolation: Creating a reference free smooth A/D conversion

Title: Webinars for Young Excellence: Interpolation: Creating a reference free smooth A/D conversion

Presenter: Prof. Akira Matsuzawa

Abstract: Conventional A/D conversion is performed by comparing the input signal voltage with the reference voltage. On the other hand, by dividing and comparing the output voltages of two amplifiers with different reference voltages with the same input signal voltage, it was found that A/D conversion can be performed. This A/D conversion method is called interpolated A/D conversion.

This conversion method enables smooth A/D conversion with a small DNL without adjusting the gain of the amplifier or the reference voltage, and also enables low power consumption by reducing the number of amplifiers.

In this talk, we will introduce not only the principles and effects of interpolated A/D conversion, but also conceptual methods in circuit development, such as generalization by intuition and formulation that gave rise to unique A/D conversion methods.

A resistive-interpolated Bi-CMOS ADC was developed for home HDTV receivers. A capacitive-interpolated CMOS ADC reduced the power consumption to 1/8 of other ADCs was developed for the portable digital video equipment such as a handy camcorder. A gate-width interpolation CMOS ADC achieved ultra-high-speed operation of 400 MS/s and 1/10 the power consumption of the other ADCs. It is embedded on the world’s first one-chip Mixed Signal SoC for DVD and contributed higher performance and lower cost of DVD recorders.

In this talk, we would like you to understand that the interpolated A/D conversion method is not just an idea but was created for the development of A/D converters with high performance and low power in order to realize the new electronic devices.

Akira Matsuzawa received B.S., M.S., and Ph.D. degrees in EE from Tohoku University, Sendai, Japan, in 1976, 1978, and 1997. In 1978, he joined Panasonic, and in 2003, joined Tokyo Institute of Technology as a full professor, and in 2018, became professor emeritus and CEO of Tech Idea. He has been developing video-rate ADCs, mixed-signal SoCs and millimeter-wave CMOS transceivers. In 2022, he received IEEE Donald. O. Pederson award in Solid-State Circuits. He is an IEEE Fellow since 2002 and Life-Fellow since 2023.

New Lab Homepage

Okada Laboratory’s website has been renewed!

IEEE SSCS Japan Chapter VDEC Design Award

Yamazaki-san won IEEE SSCS Japan Chapter VDEC Design Award!!

Prof. Inchan Ju

Prof. Inchan Ju visited our lab!

Graduation Ceremony

Congratulations on completing your Master’s degree! Keep up the good work in your PhD study!

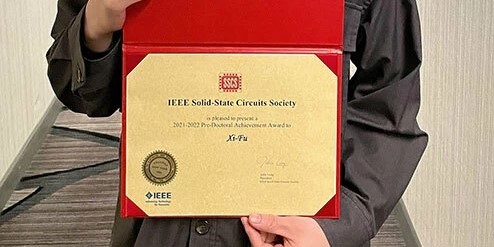

Xi FU won the IEEE SSCS Predoctoral Achievement Award

Xi FU, a doctoral course student, won this-year’s IEEE SSCS Predoctoral Achievement Award. This award is for recognizing his outstanding achievement based on the aveacademic record and promise, quality of publications.

Preparing the Stage for 6G: A Fast and Compact Transceiver for Sub-THz Frequencies

published onProf. Bogdan Staszewski

Prof. Bogdan Staszewski came to our lab at June 9th, 2023!

Welcome!!!

Prof. Kenneth O

Prof. Kenneth O came to our lab at June 7th, 2023! Welcome!!!