### A 0.0066mm<sup>2</sup> 780µW Fully Synthesizable PLL with a Current Output DAC and an Interpolative Phase-Coupled Oscillator using Edge Injection Technique

Wei Deng, Dongsheng Yang, Tomohiro Ueno, Teerachot Siriburanon, Satoshi Kondo, Kenichi Okada, and Akira Matsuzawa

### Tokyo Institute of Technology, Japan

### Outline

- Motivation

- Concept of synthesizable analog circuits

- Synthesizable PLL

- Interpolative phase-coupled oscillator

- Standard-cell I-DAC

- Standard-cell varactor

- Edge injection

- Measurement Results

- Conclusion

### Motivation

- Synthesizable analog circuits

- Portability

- Scalability

- Layout issues above 20nm

- Potential applications

- PLL

- ADC, DAC

- Wireless/Wireline transceivers

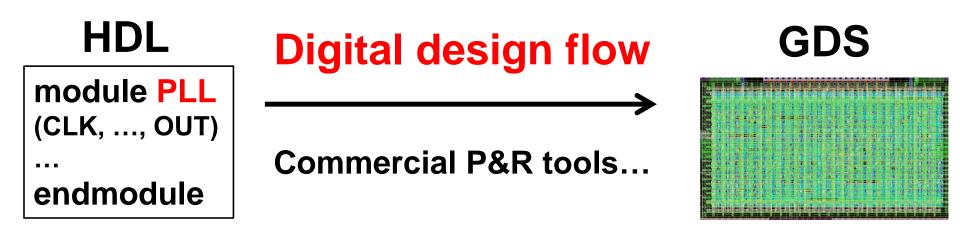

# Synthesizable Analog Circuits

### with a standard-cell library without any custom-designed cells without manual placement

### **Issue: Layout Uncertainty**

**Ideal placement**

**Actual placement**

Unbalanced loading

No layout symmetry

### A new analog-circuit architecture is required, which tolerates layout impairment/uncertainty.

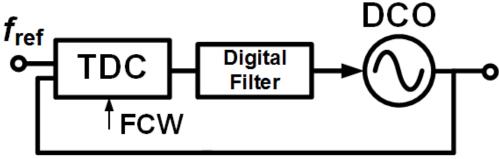

# **Conventional All-digital PLLs**

TDC-based architecture

- -The layout uncertainty degrades TDC and DCO linearity.

- Poor frequency resolution by standard-cell design.

- Trade-off between layout integrity and jitter performance

# **Proposed Synthesizable PLL**

- Injection-locking topology

- Avoid TDC issues (linearity, power-resolution trade-off)

- Circuit techniques

- Interpolative phase-coupled osc. & I-DAC

- Overcome phase imbalance

- A new varactor for fine resolution

- Low spur level

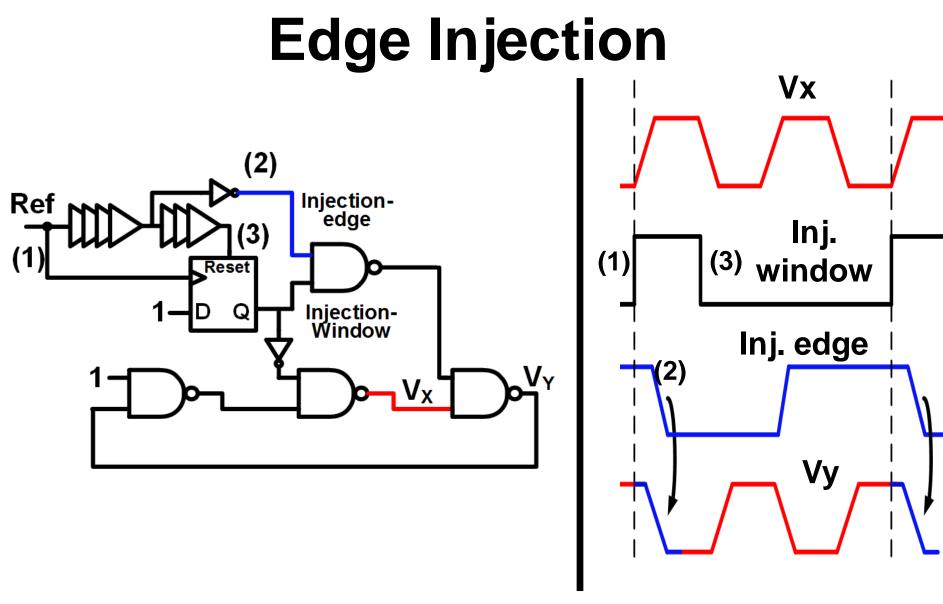

- Edge injection technique

- Relax severe timing design

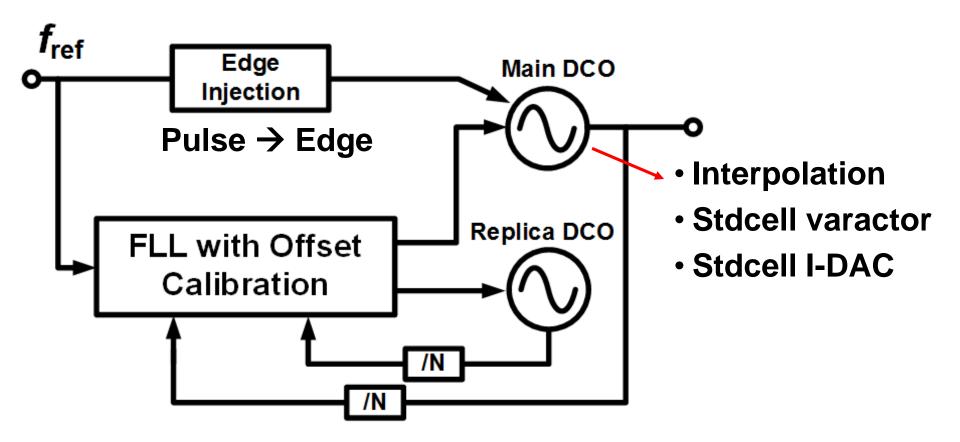

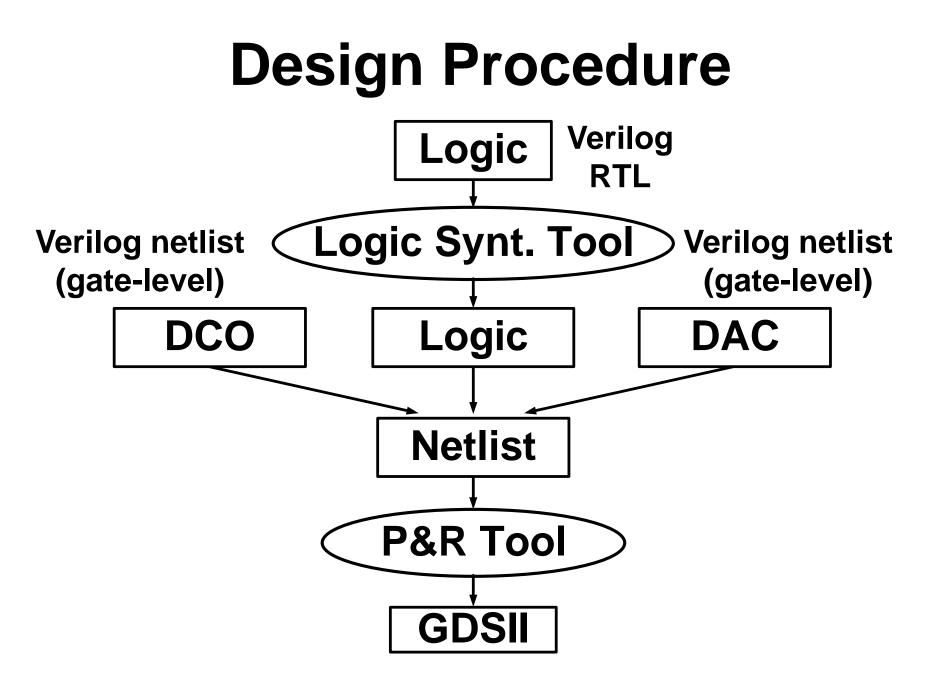

### **TOP Block Diagram**

[W. Deng, et al., ISSCC 2013]

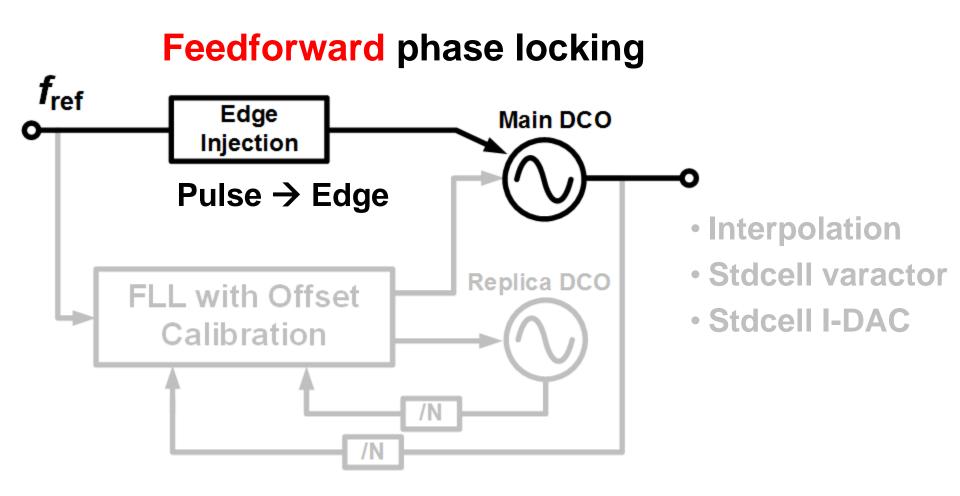

### **TOP Block Diagram**

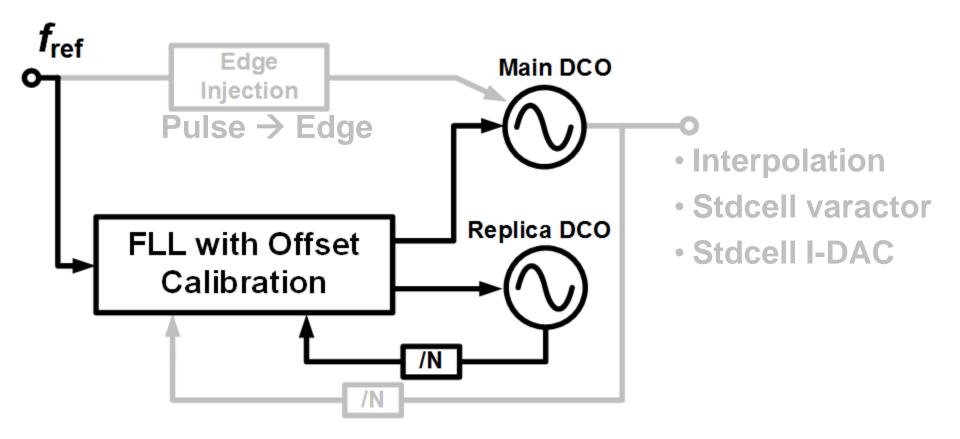

### **TOP Block Diagram**

#### **Feedback FLL** for frequency tracking

[W. Deng, et al., ISSCC 2013]

### Outline

- Motivation

- Concept of synthesizable analog circuits

- Synthesizable PLL

- Interpolative phase-coupled oscillator

- Standard-cell I-DAC

- Standard-cell varactor

- Edge injection

- Measurement Results

- Conclusion

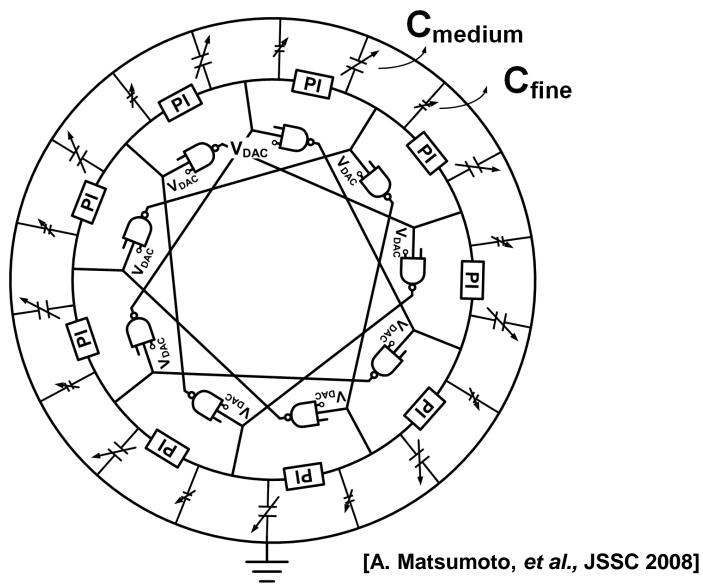

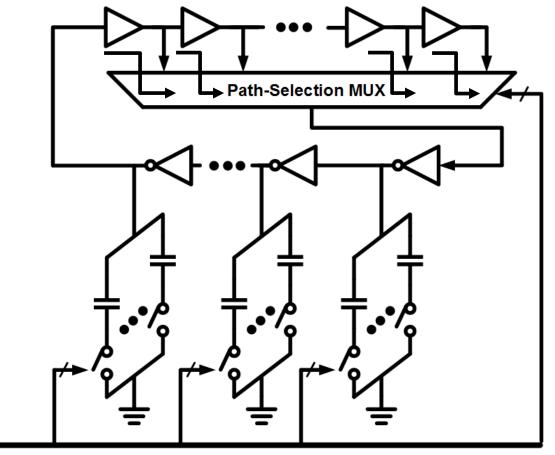

### **Block Diagram of DCO**

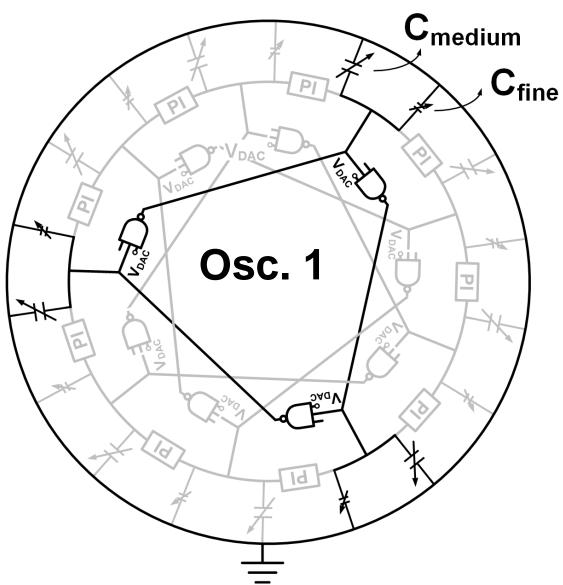

### **Block Diagram of Oscillator 1**

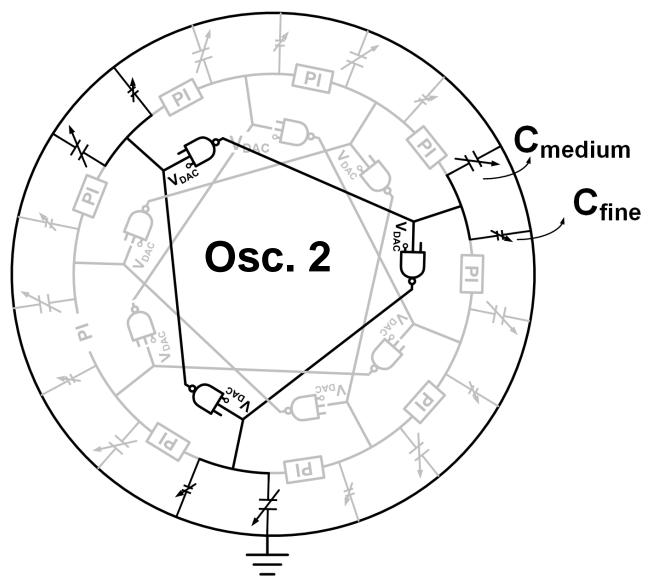

### **Block Diagram of Oscillator 2**

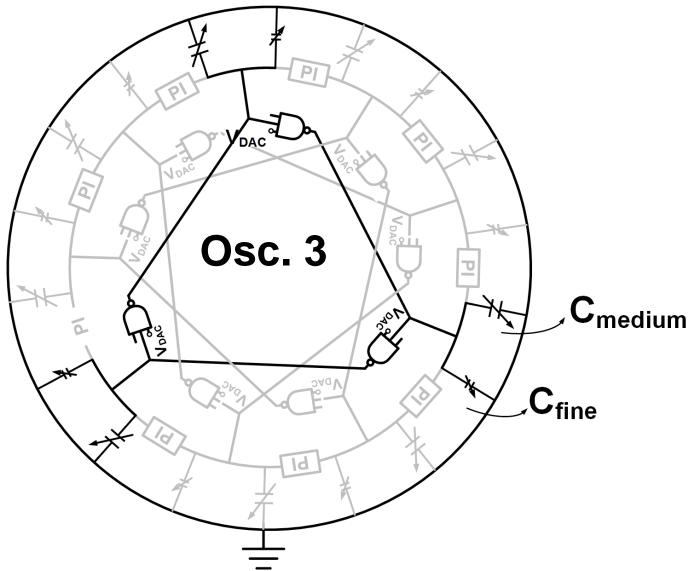

### **Block Diagram of Oscillator 3**

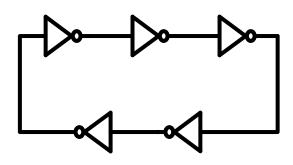

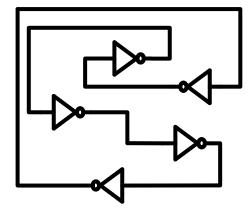

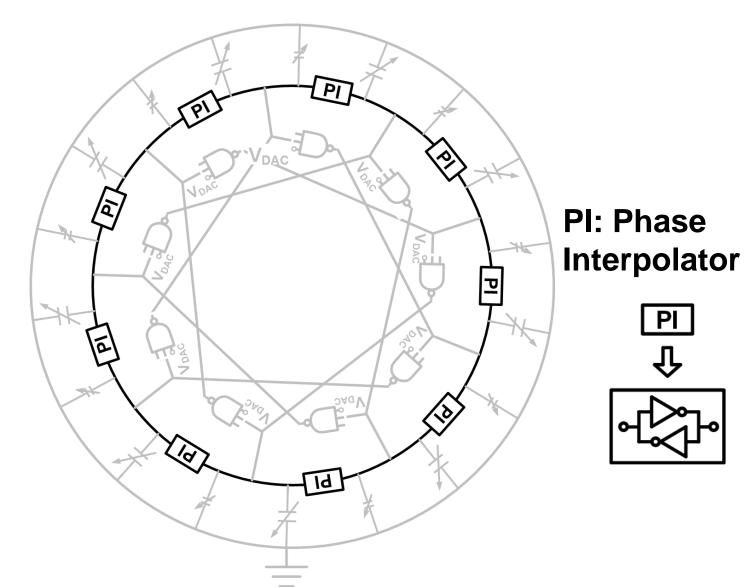

### **Interpolative Phase-coupled Ring**

### Outline

- Motivation

- Concept of synthesizable analog circuits

- Synthesizable PLL

- Interpolative phase-coupled oscillator

- Standard-cell I-DAC

- Standard-cell varactor

- Edge injection

- Measurement Results

- Conclusion

### **Conventional Coarse Tuning**

#### Unbalanced loading at each stage.

#### **Control code**

[D. Sheng, et al., TCAS II 2007]

© 2014 IEEE International Solid-State Circuits Conference

### **Coarse Tuning using DAC**

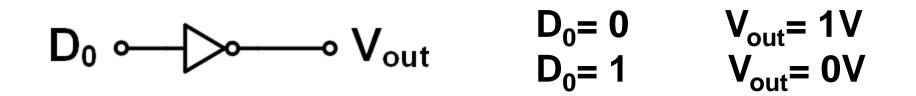

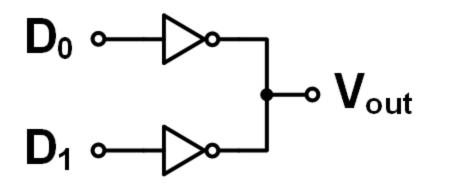

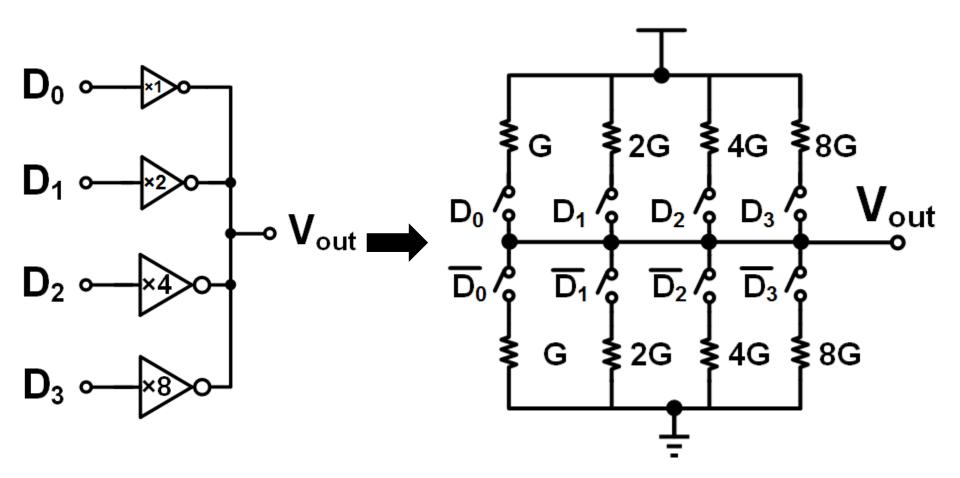

### Simple Voltage-output DAC

$$\begin{array}{lll} D_0 D_1 = 11 & V_{out} = 0V \\ D_0 D_1 = 10 & V_{out} = 0.5V \\ D_0 D_1 = 01 & V_{out} = 0.5V \\ D_0 D_1 = 00 & V_{out} = 1V \end{array}$$

### **Model of V-linear DAC**

#### • How to obtain a I-linear DAC?

© 2014 IEEE International Solid-State Circuits Conference

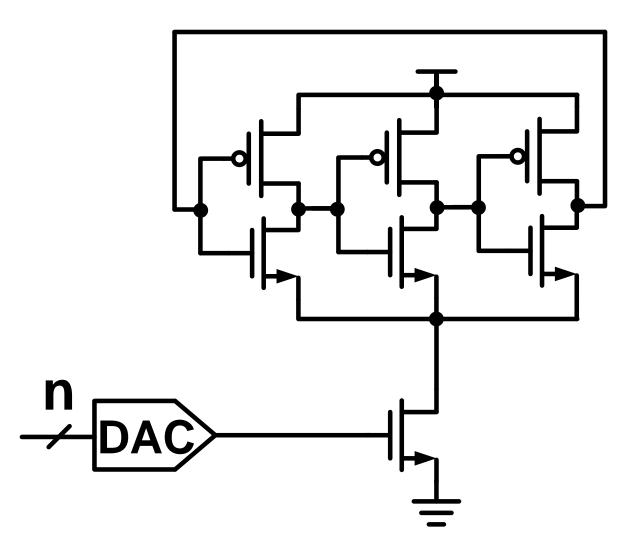

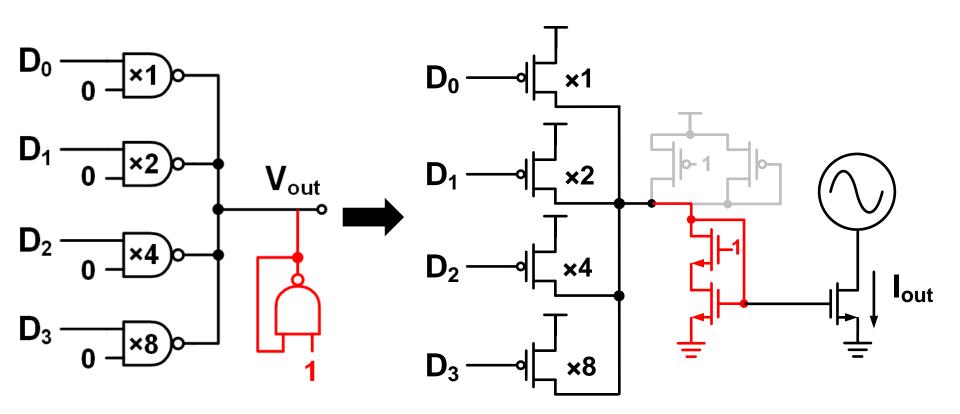

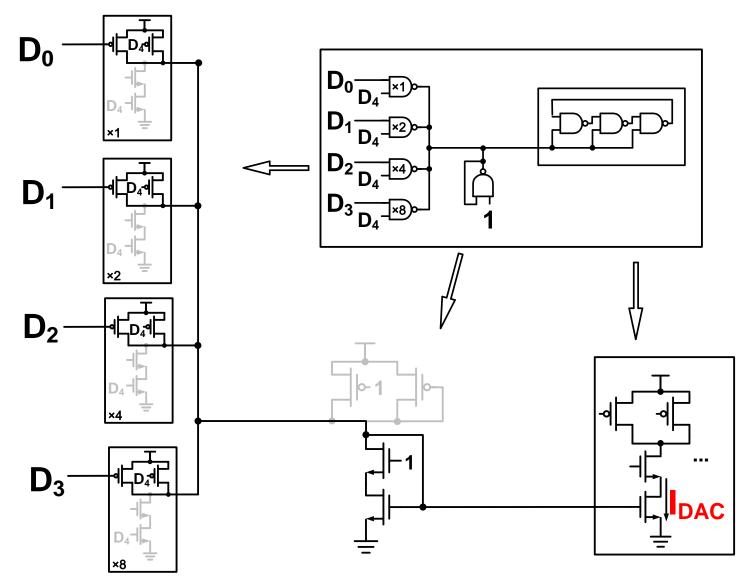

### **Proposed I-linear DAC**

### • A feedback structure for forming a <u>current mirror</u>.

© 2014 IEEE International Solid-State Circuits Conference

### **Proposed I-linear DAC (cont.)**

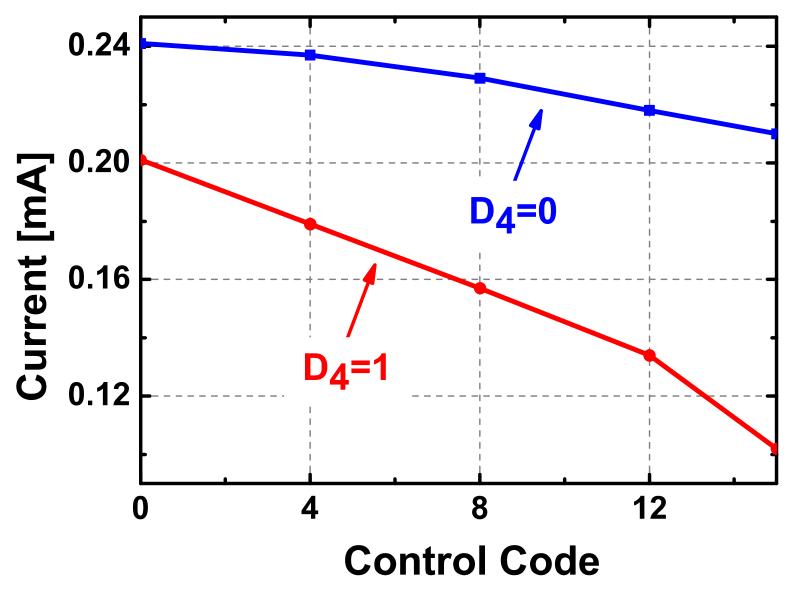

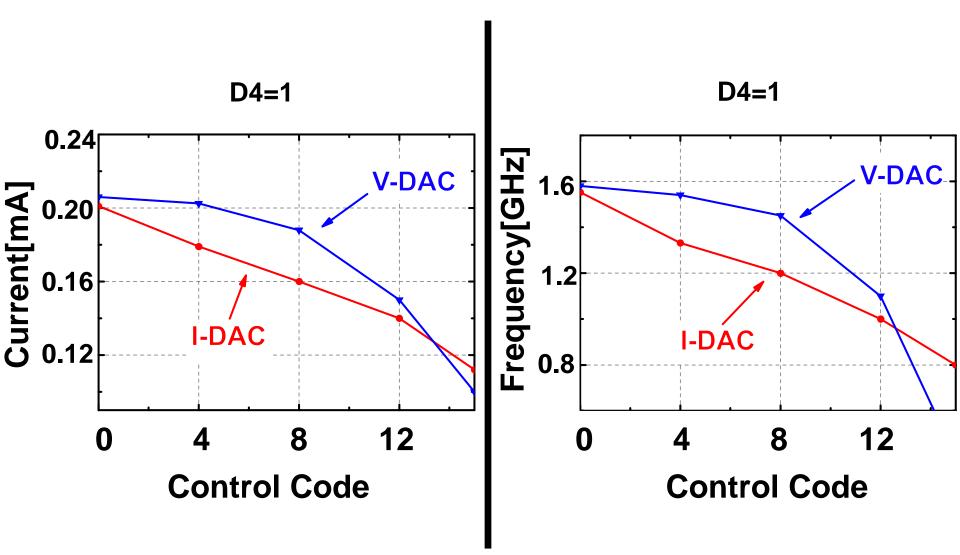

### **Simulation Result**

### **V-DAC VS I-DAC**

### Outline

- Motivation

- Concept of synthesizable analog circuits

- Synthesizable PLL

- Interpolative phase-coupled oscillator

- Standard-cell I-DAC

- Standard-cell varactor

- Edge injection

- Measurement Results

- Conclusion

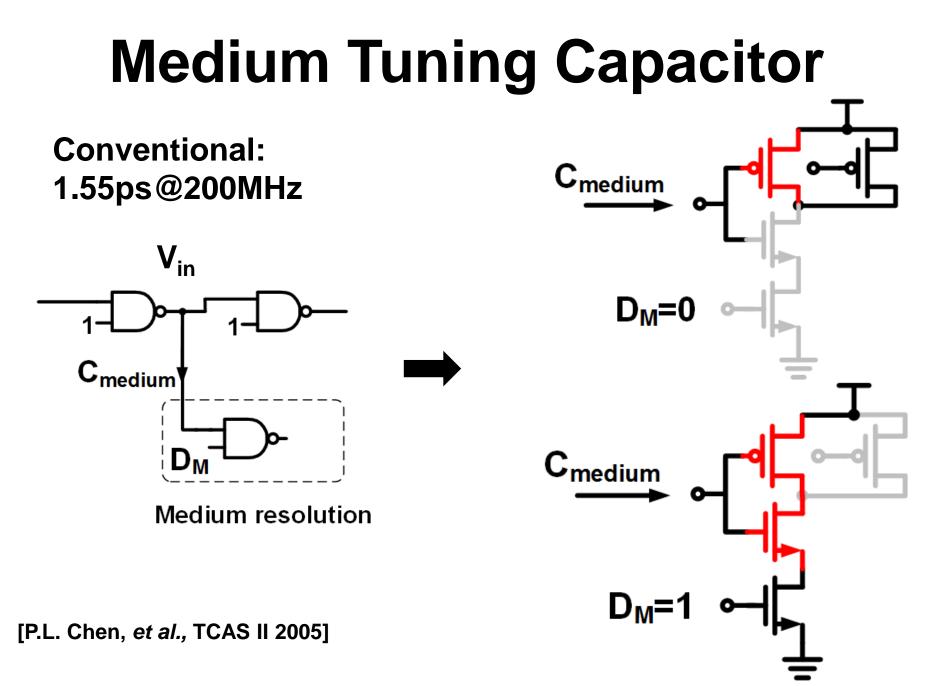

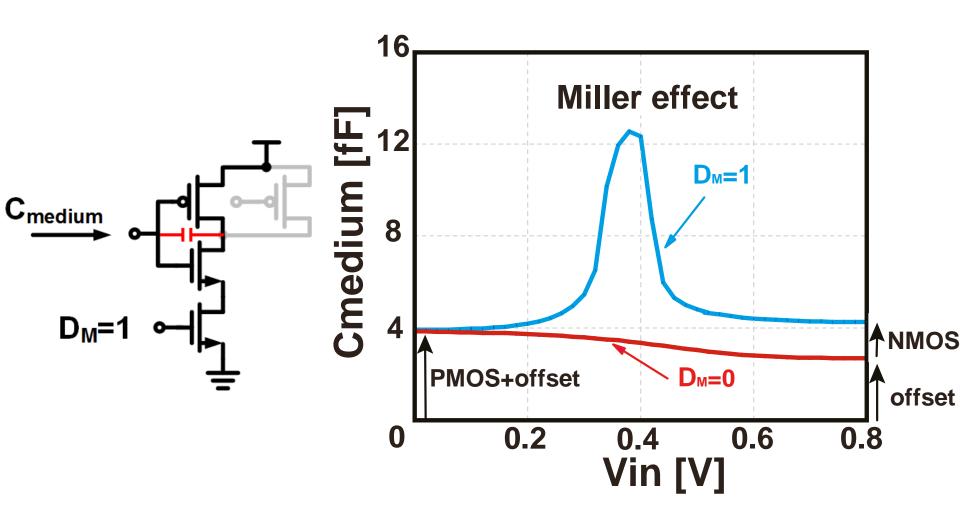

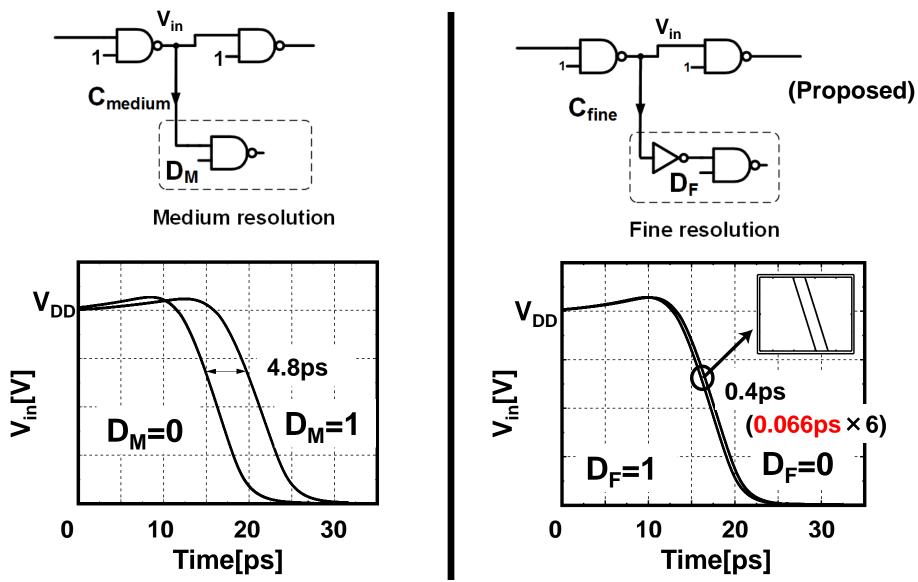

# Simulated C<sub>medium</sub> against V<sub>in</sub>

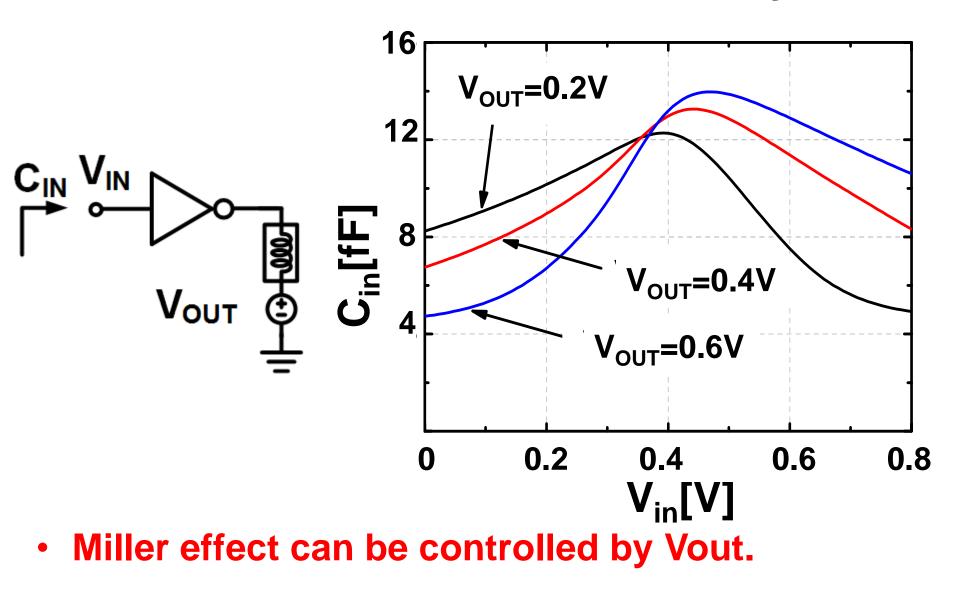

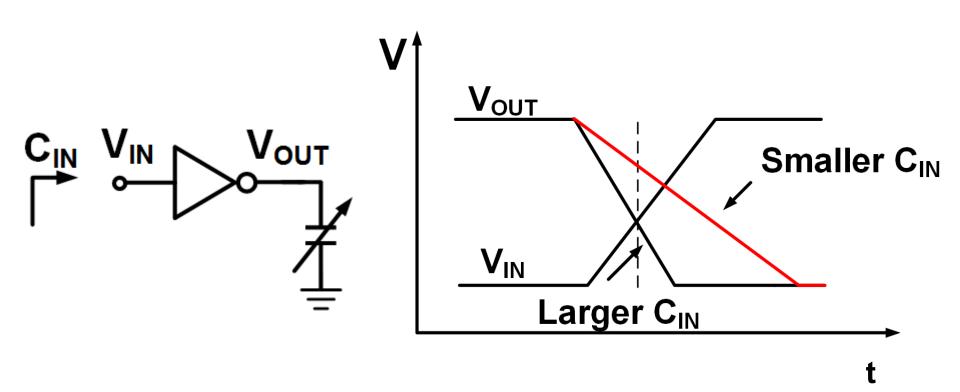

### **Miller Effect Sensitivity**

### Miller Effect Sensitivity (Cont.)

# • A transient variation of Vout can make a fine capacitance difference in CIN.

### **Tuning Capacitors**

© 2014 IEEE International Solid-State Circuits Conference

### Outline

- Motivation

- Concept of synthesizable analog circuits

- Synthesizable PLL

- Interpolative phase-coupled oscillator

- Standard-cell I-DAC

- Standard-cell varactor

- Edge injection

- Measurement Results

- Conclusion

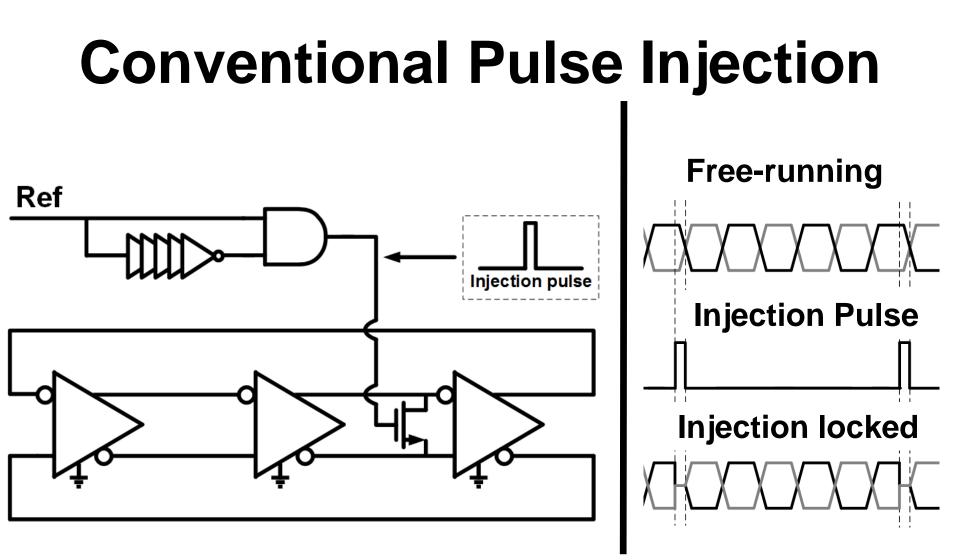

Severe timing design is required on the injection pulse width.

[B. Helal, et al., JSSC 2009]

#### Severe timing design is not required.

© 2014 IEEE International Solid-State Circuits Conference

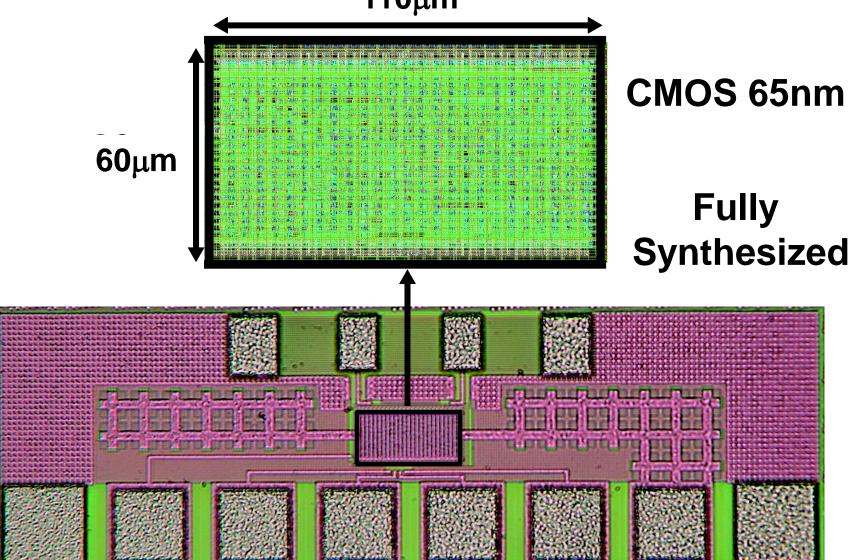

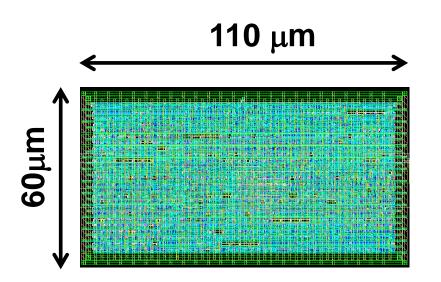

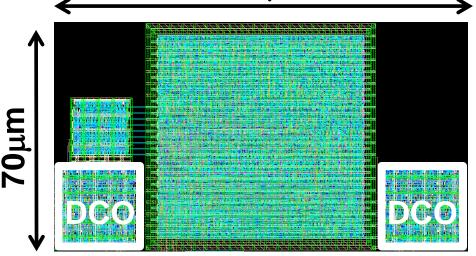

### Chip Microphotograph 110µm

© 2014 IEEE International Solid-State Circuits Conference

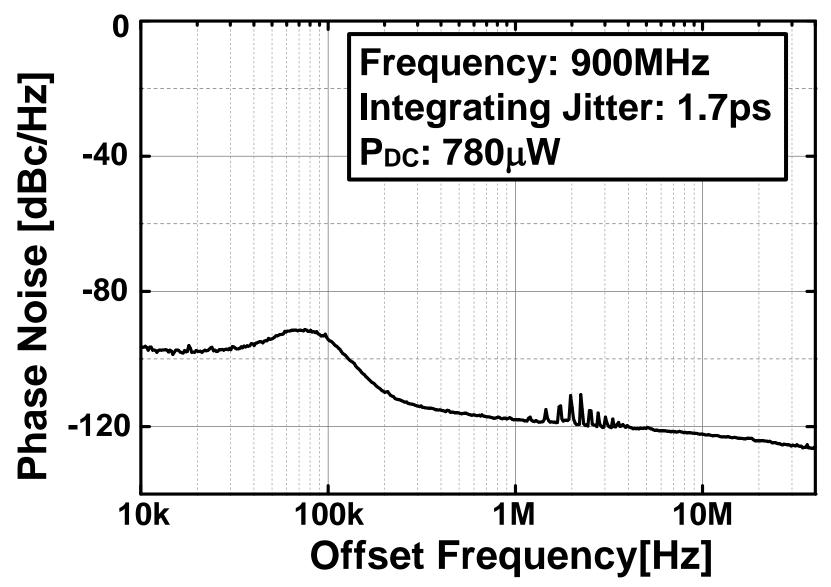

### **Phase Noise**

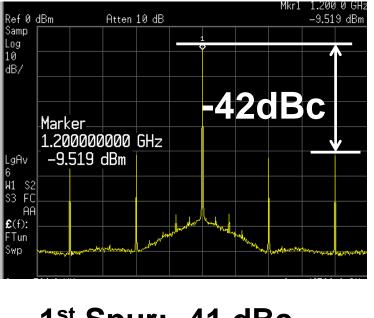

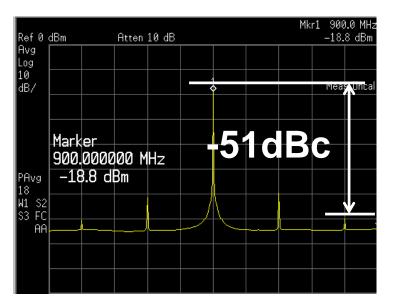

### **Measured Spur Level**

#### Pulse Injection (Conventional) N=6

1<sup>st</sup> Spur: -41 dBc 2<sup>nd</sup> Spur: -42 dBc

#### Edge Injection (This work) N=6

1<sup>st</sup> Spur: -41 dBc 2<sup>nd</sup> Spur: -51 dBc

**N: Multiplication factor**

### **Layout Consideration**

#### Integrating Jitter: 1.7ps P<sub>DC</sub>: 780μW FOM: -236.5 dB

# Fully synthesized (proposed)

Integrating Jitter: 2.32ps P<sub>DC</sub>: 640μW FOM: -234.6 dB

**130** μm

### Hierarchical P&R with synthesized DCOs

© 2014 IEEE International Solid-State Circuits Conference

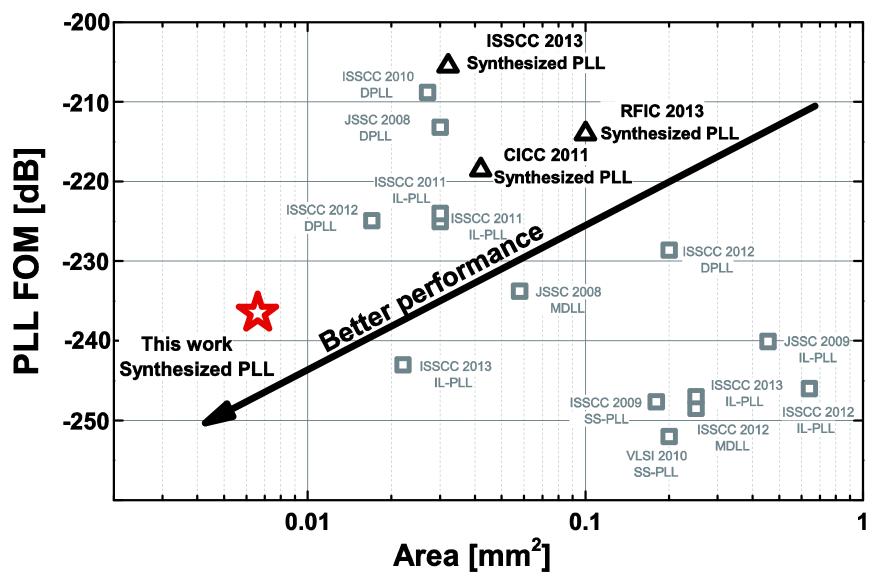

# **Compar. of Synthesizable PLLs**

|                            | This work   | [1]         | [2]      | [3]      |

|----------------------------|-------------|-------------|----------|----------|

|                            | <u>65nm</u> | <b>28nm</b> | 65nm     | 65nm     |

| Power                      | 0.78        | 13.7        | 3.1      | 2.1      |

| [mW]                       | @900MHz     | @2.5GHz     | @250MHz  | @403MHz  |

| Area<br>[mm <sup>2</sup> ] | 0.0066      | 0.042       | 0.032    | 0.1      |

| Integ.<br>Jitter [ps]      | 1.7         | N.A.        | 30       | N.A.     |

| RMS<br>Jitter [ps]         | 2.8         | 3.2         | N.A.     | 13.3     |

| FOM [dB]                   | -236.5      | -218.6*     | -205.5   | -214*    |

| W/ custom cells?           | No          | No          | Yes      | Yes      |

| Topology                   | IL-base     | TDC-base    | TDC-base | TDC-base |

\*FOM is calculated based on RMS jitter.

© 2014 IEEE International Solid-State Circuits Conference

### **Performance Comparison**

### Conclusion

- Synthesizable analog circuit design is proposed.

- By the digital design flow

- Without any manual placement

- Without any custom-designed cells

- Fully synthesized PLL

- Dual-loop injection-lock topology

- Current-output DAC

- Ultra-fine frequency resolution

- Interpolative-phase coupled oscillator

### Acknowledgement

This work was partially supported by STARC, SCOPE, MIC, MEXT, Canon Foundation, and VDEC in collaboration with Synopsys, Inc., Cadence Design Systems, Inc., and Agilent Technologies Japan, Ltd.