# An HDL-Synthesized Gated-Edge-Injection PLL with A Current Output DAC

Dongsheng Yang, Wei Deng, Tomohiro Ueno, Teerachot Siriburanon, Satoshi Kondo, Kenichi Okada, and Akira Matsuzawa

Tokyo Institute of Technology, Japan

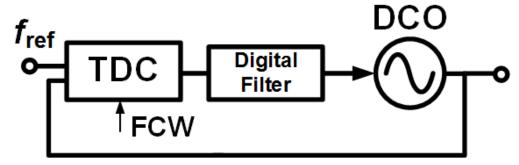

### **Conventional All-digital PLLs**

TDC-based architecture

- The layout uncertainty degrades TDC and DCO linearity.

- Trade-off between layout area and jitter performance

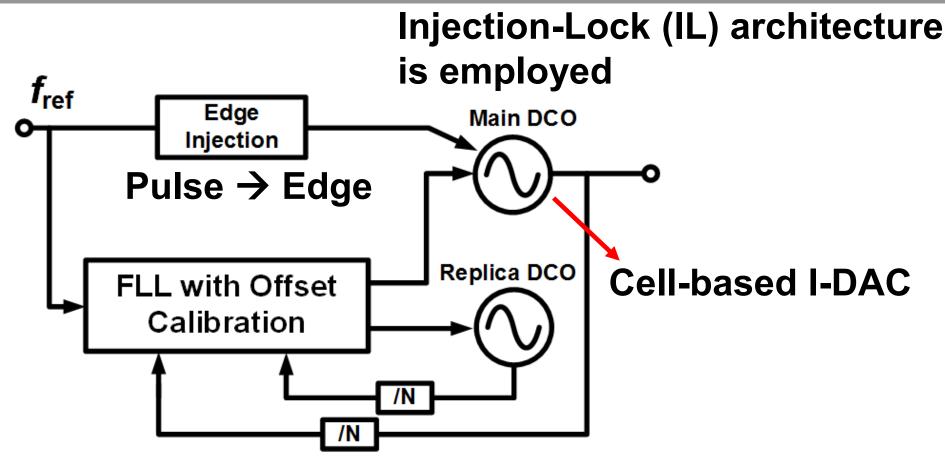

#### Proposed IL-based Synthesizable PLL

Feedback FLL for frequency tracking Feedforward edge injection for phase locking

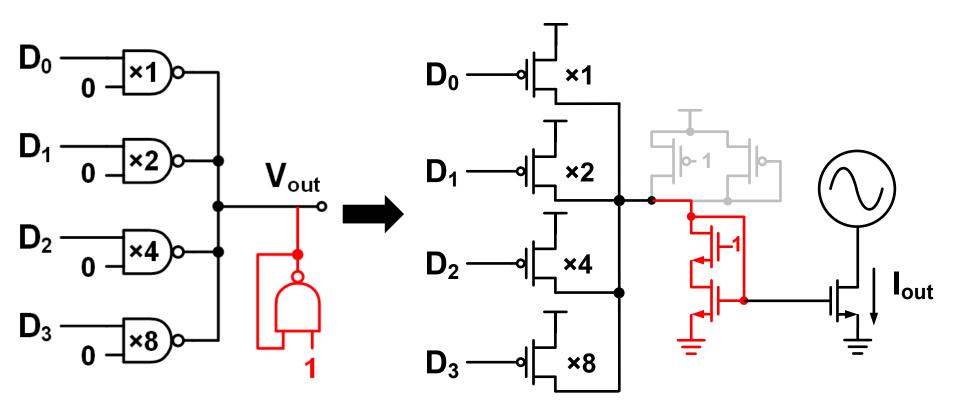

## **Proposed Current-linear DAC**

A feedback structure for forming a current mirror.

#### Performance Comparison

|                  | This work<br>65nm | [1]<br>28nm     | [2]<br>65nm    | [3]<br>65nm    |

|------------------|-------------------|-----------------|----------------|----------------|

| Power<br>[mW]    | 0.78<br>@900MHz   | 13.7<br>@2.5GHz | 3.1<br>@250MHz | 2.1<br>@403MHz |

| Area<br>[mm²]    | 0.0066            | 0.042           | 0.032          | 0.1            |

| FOM [dB]         | -236.5            | -218.6*         | -205.5         | -214*          |

| W/ custom cells? | No                | No              | Yes            | Yes            |

| Topology         | IL-base           | TDC-base        | TDC-base       | TDC-base       |

<sup>\*</sup>FOM is calculated based on RMS jitter.

The proposed HDL-synthesized PLL can achieve the smallest area with comparable FOM.