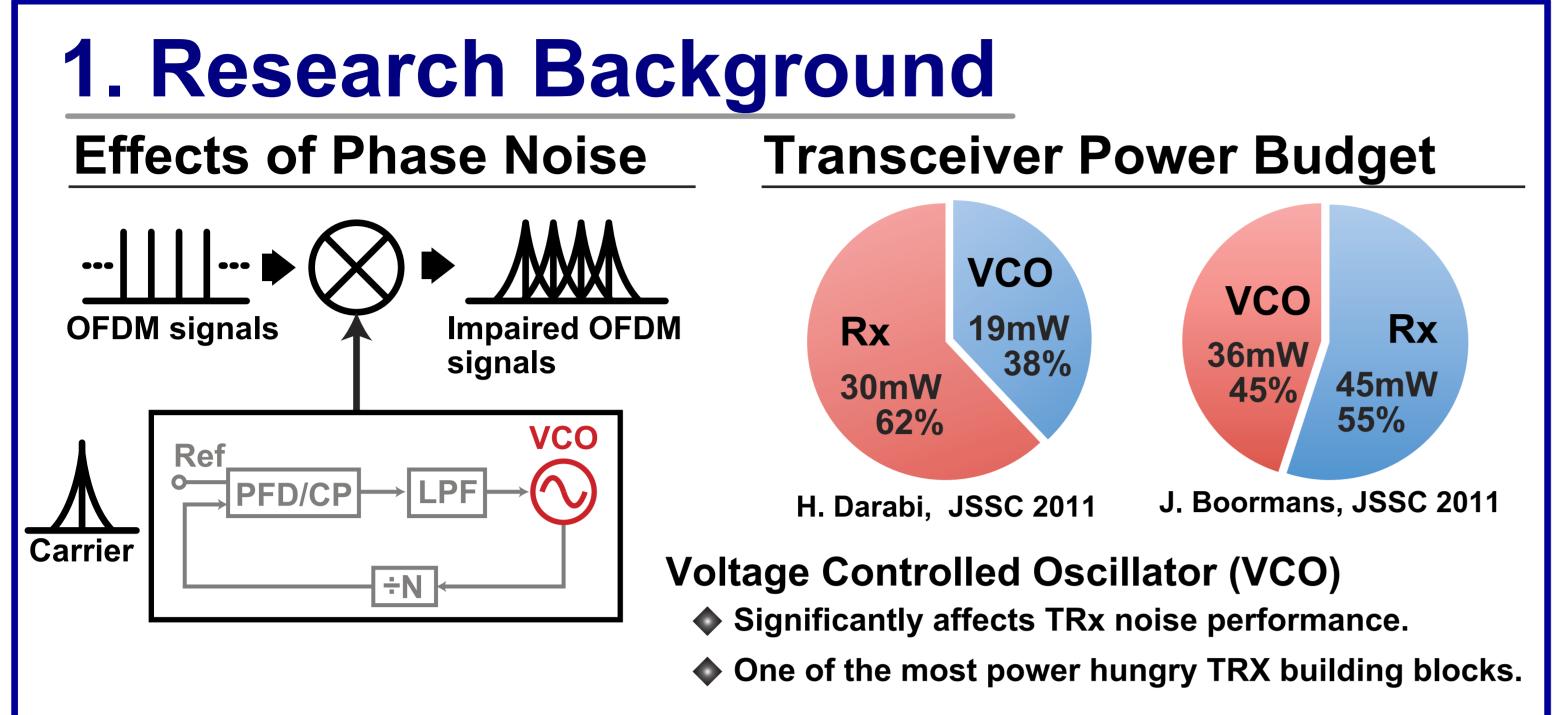

# <sup>15-19</sup> A Tail-Current Modulated VCO with Adaptive-Bias Scheme Aravind Tharayil Narayanan, Wei Deng, Kenichi Okada, Akira Matsuzawa Tokyo Institute of Technology, Japan

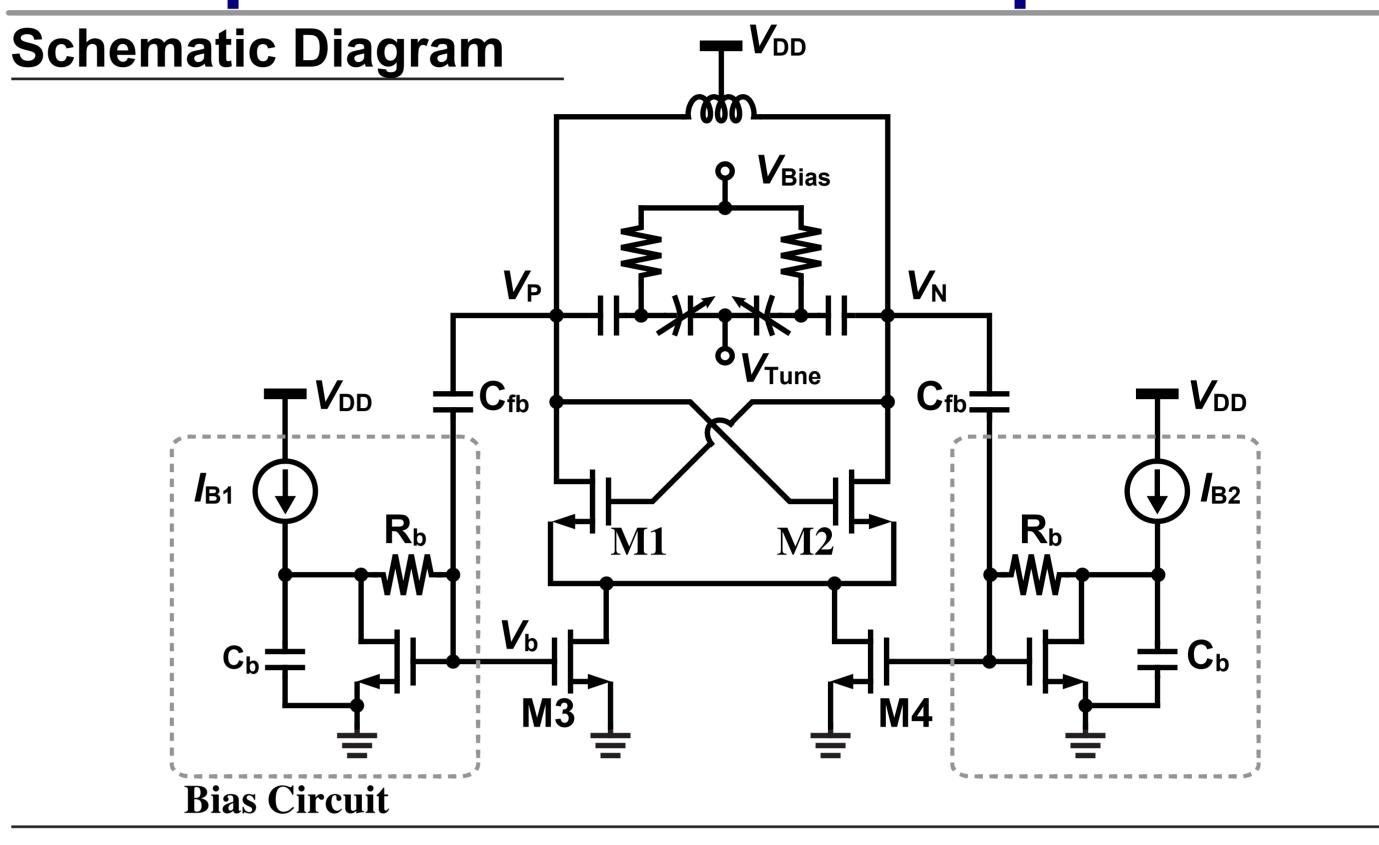

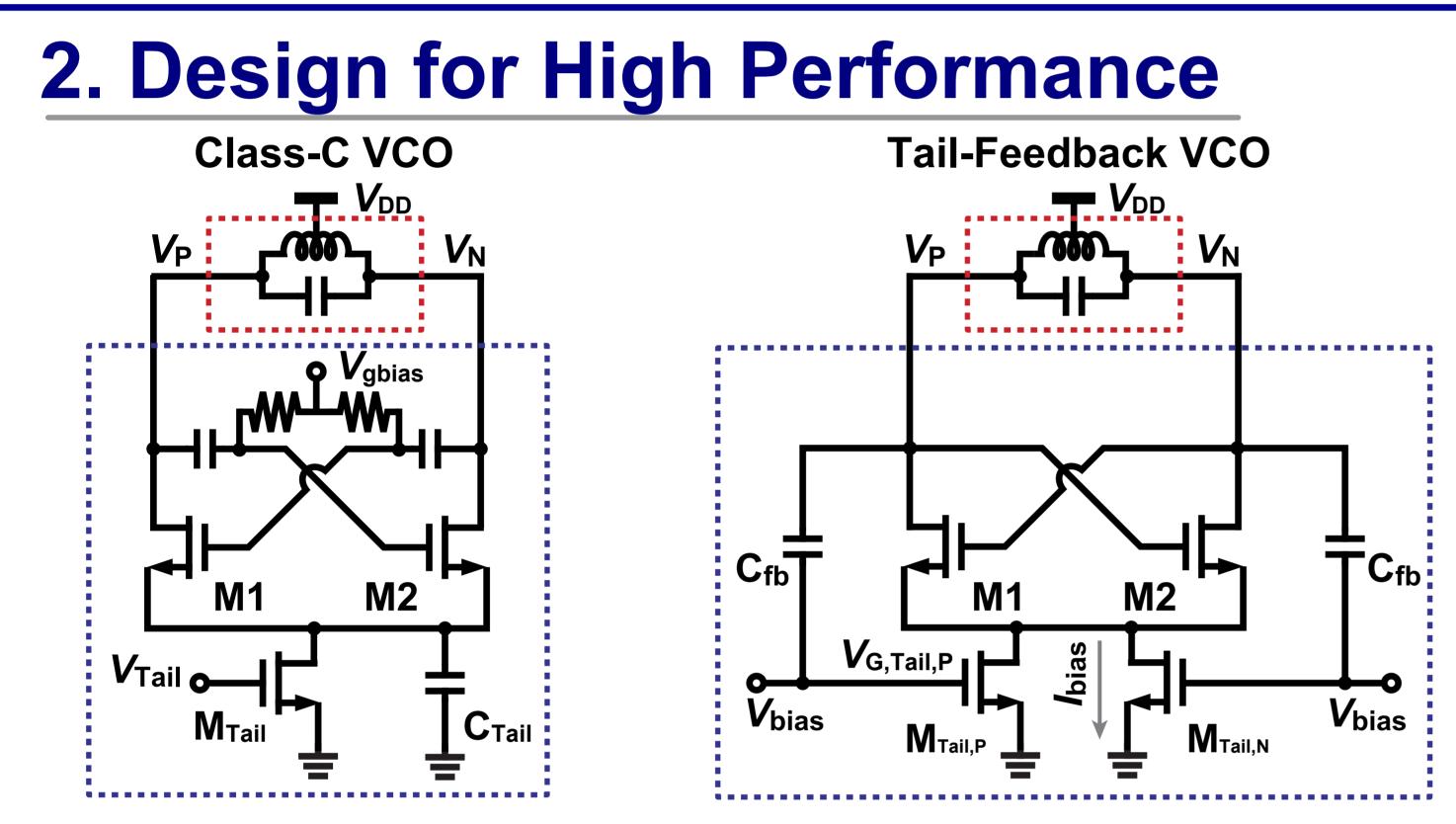

#### 4. Proposed VCO with Adaptive-Bias

AIM: High performance VCO with minimum area/power overhead.

#### **Simulaion Results**

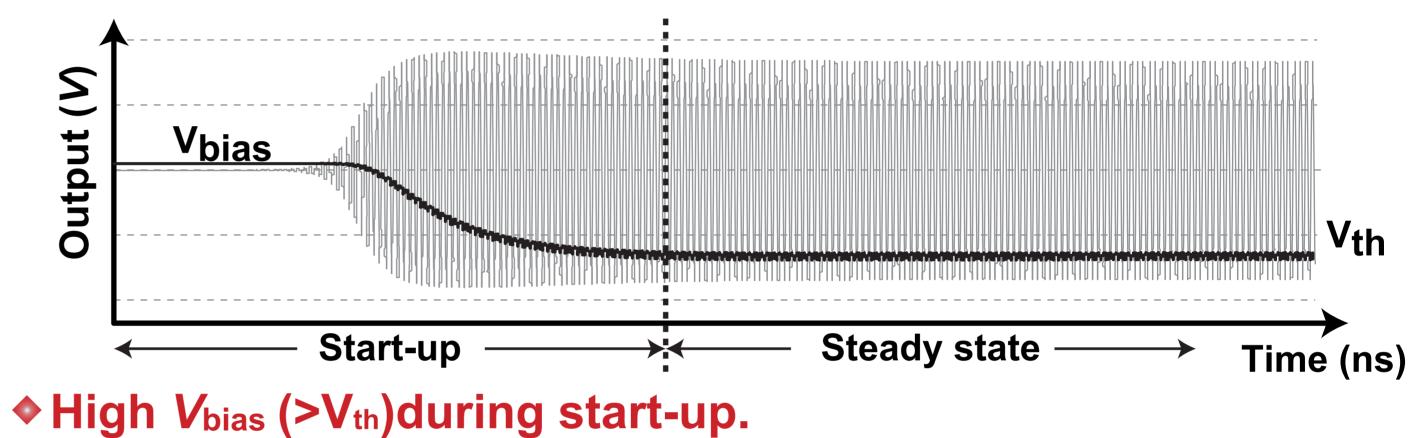

◆ *V*<sub>bias</sub> is gradually reduced for optimum enhancing efficiency.

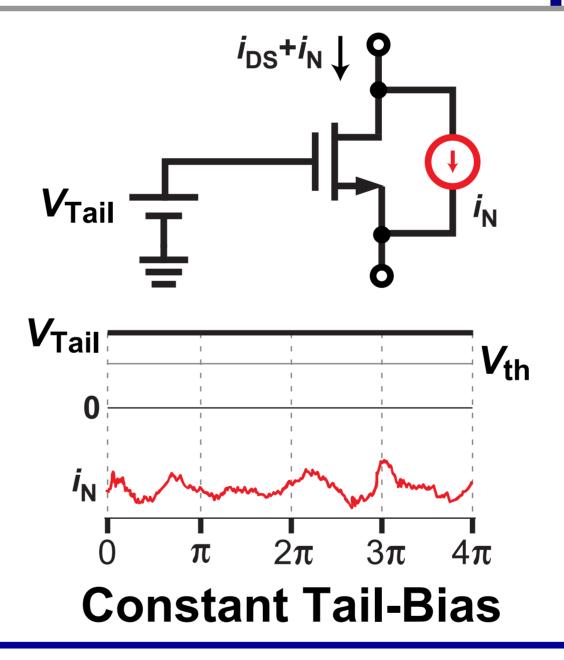

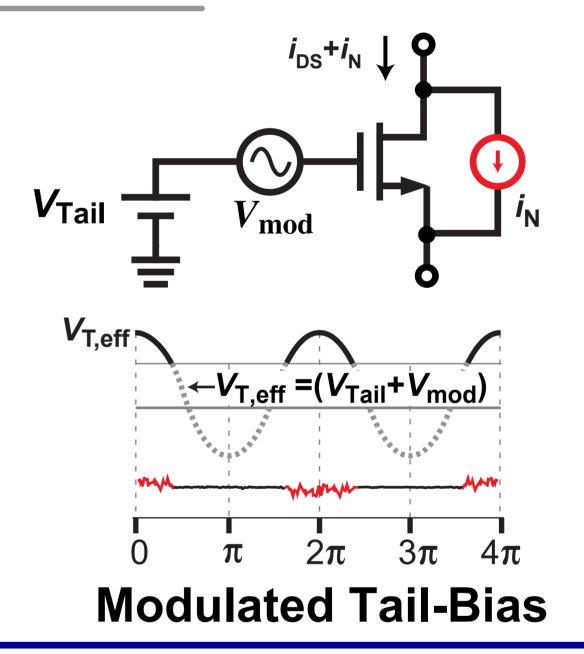

### 5. Tail-Noise Suppression

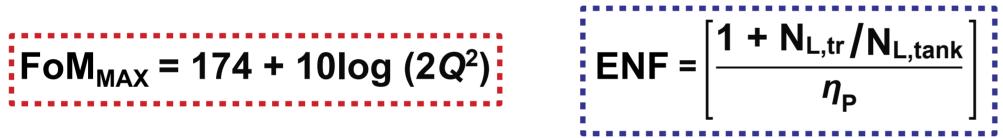

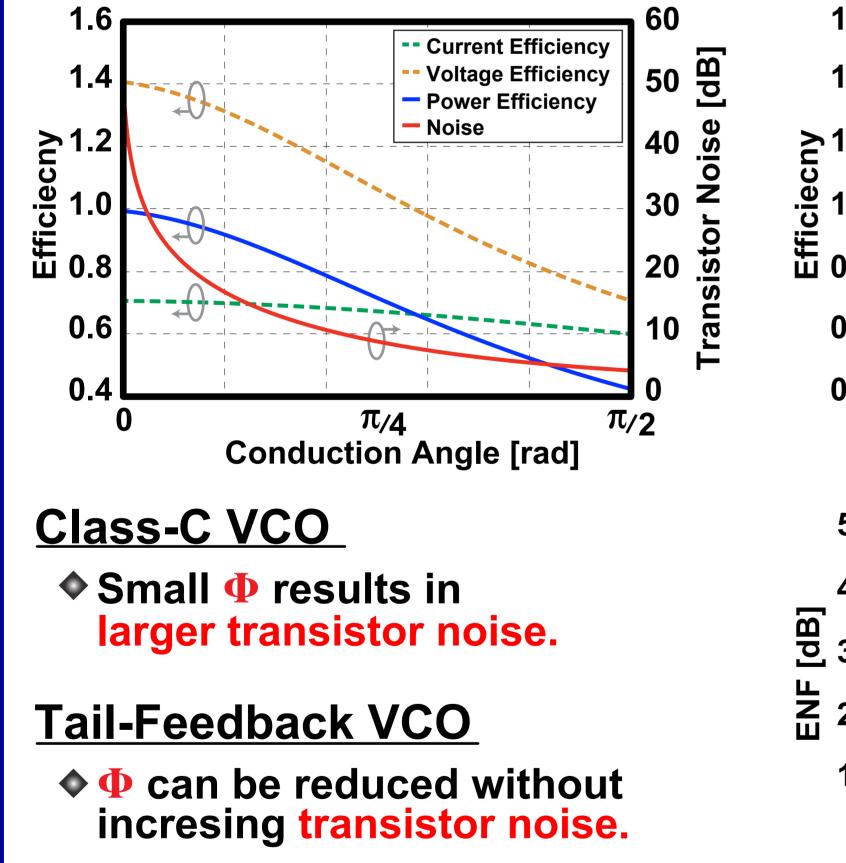

Isolating the noise generated by active circuitry facilitates fair comparison of various VCO architectures.

$ENF = FoM_{MAX} - FoM$

## 6. Results and Conclusions

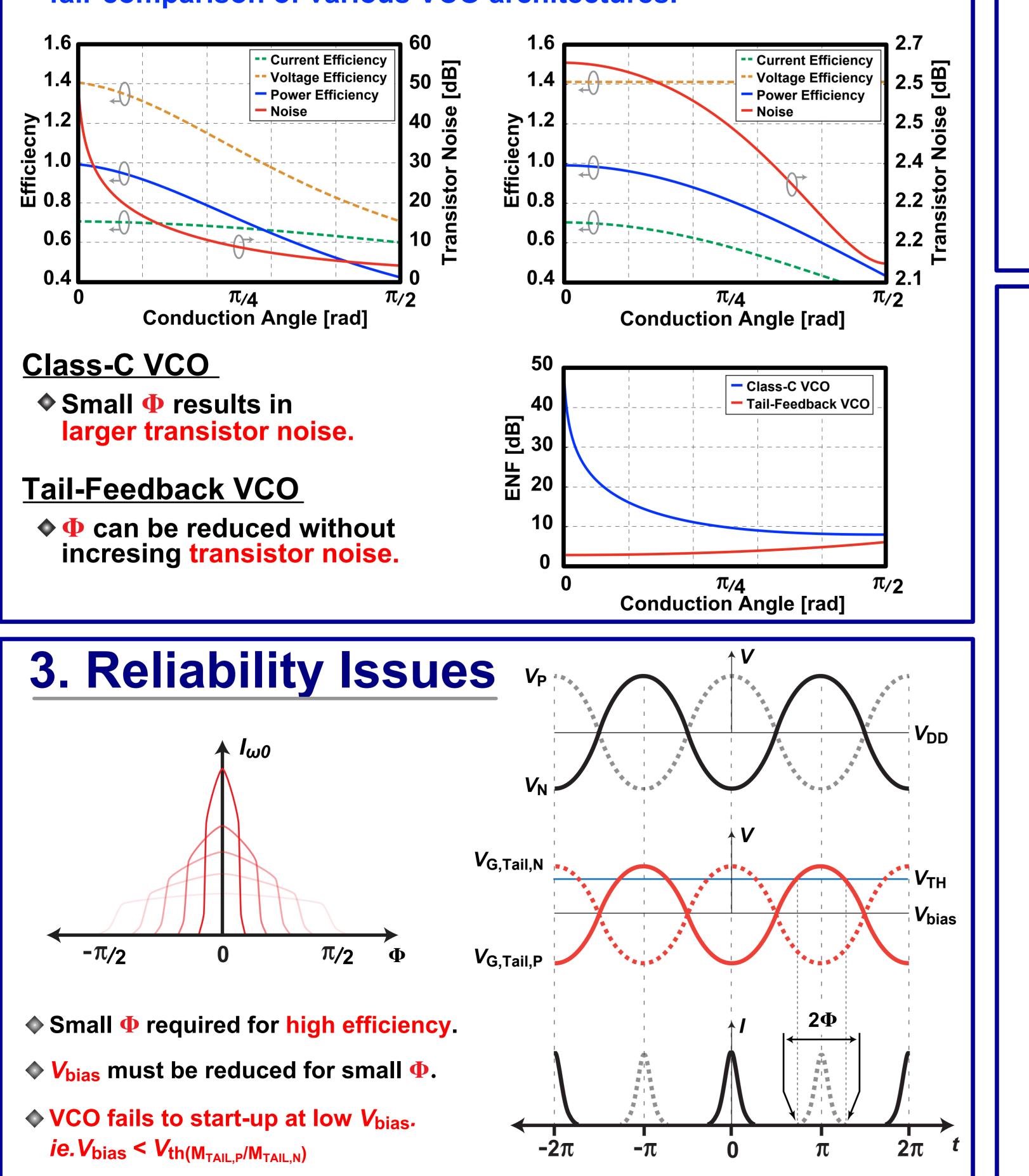

- The proposed adaptive start-up scheme achieves:

- ▶ Reliable start-up.

- Enhanced DC-RF conversion efficiency.

- These goals are achieved with very little overhead.

|             | CMOS Process | Frequency[GHz] | Phase Noise [dBc/Hz] | Pdc[mW] | FoM [dBc/Hz] |

|-------------|--------------|----------------|----------------------|---------|--------------|

| JSSC2006    | 250nm        | 1.75           | -125@1MHz            | 2.25    | -186         |

| VLSI2009    | 180nm        | 4.50           | -109@1MHz            | 0.16    | -190         |

| JSSC2013    | 180nm        | 4.84           | -125@1MHz            | 3.40    | -193         |

| This Work   |              |                |                      |         |              |

| Simulation  | 180nm        | 4.80           | -124@1Mhz            | 7.20    | -189         |

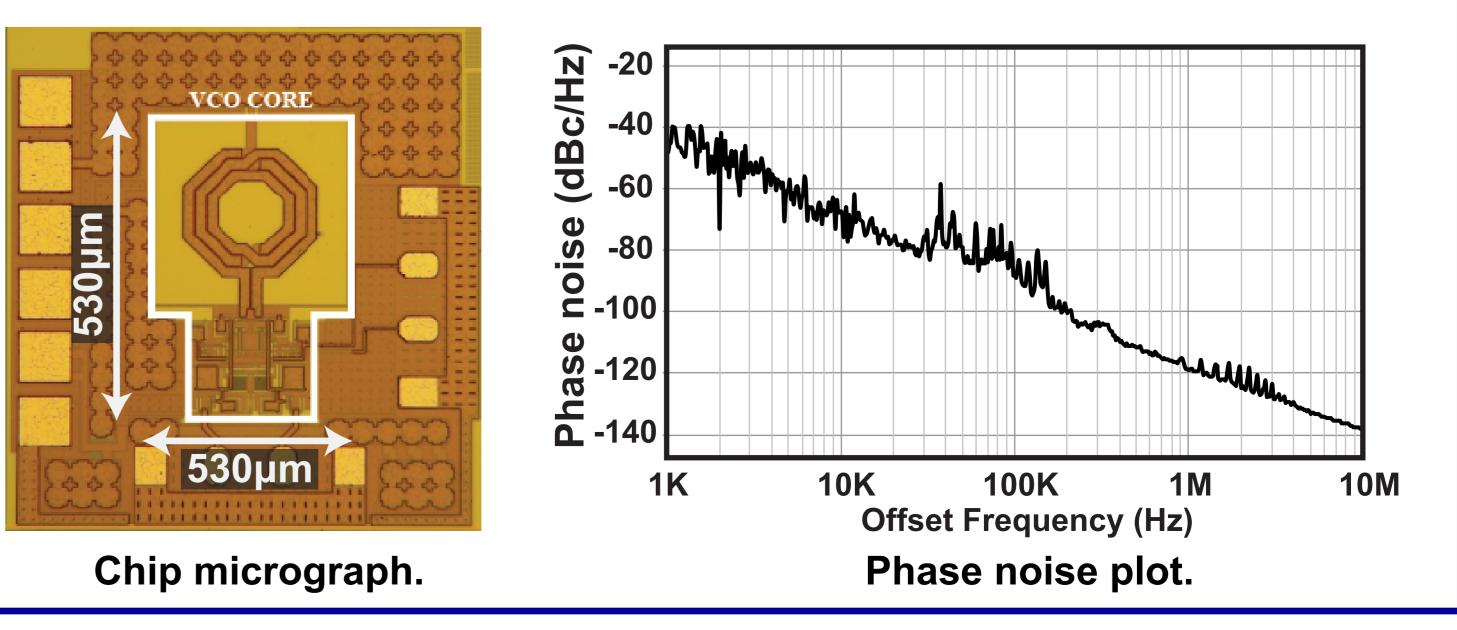

| Measurement | 180nm        | 4.60           | -119@1MHz            | 6.80    | -184         |

#### **Performance comparison.**