#### A 0.011mm<sup>2</sup> PVT-Robust Fully-Synthesizable CDR with a Data Rate of 10.05 Gb/s in 28nm FD SOI

Aravind Tharayil Narayanan, Wei Deng, Yang Dongshen, Wu Rui, Kenichi Okada and Akira Matsuzawa

#### Tokyo Institute of Technology, Japan

## Outline

- Motivation

- Architecture for Synthesis

- -Edge Injection

- -Interpolative Phase-Coupled DCO

- -Standard Cell I-DAC

- **–PVT Calibration**

- Measurement Results

- Summary

## Motivation

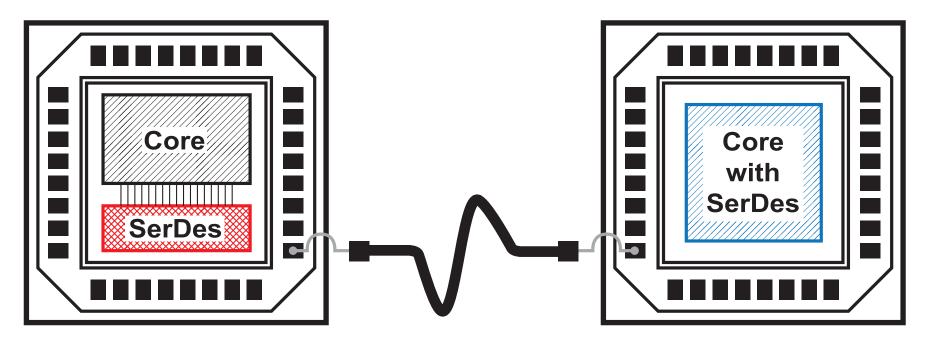

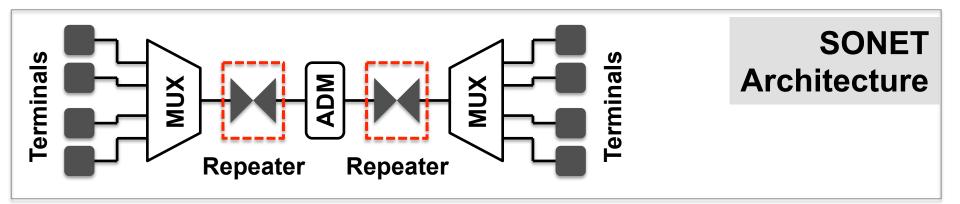

Chip-to-chip serial data link

#### Synthesizable CDR

- Co-Synthesizable with digital core.

- Scalable.

- > Portable.

#### **Advantages of Synthesis**

High level of automation saves precious resources

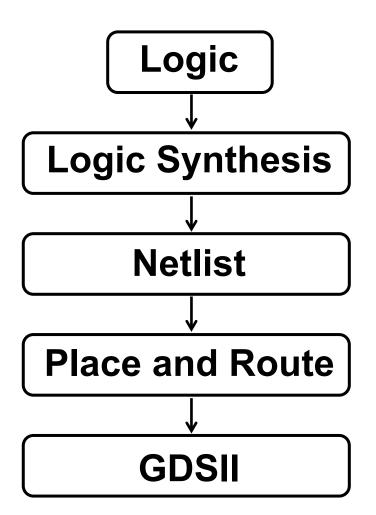

#### **Issue: Layout Uncertainty**

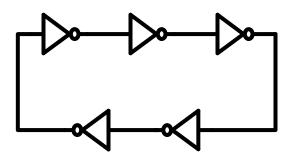

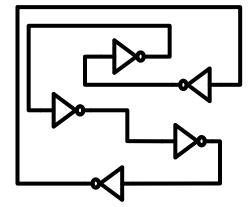

**Ideal placement**

Actual placement →No layout symmetry

# Unbalanced layout degrades system performance.

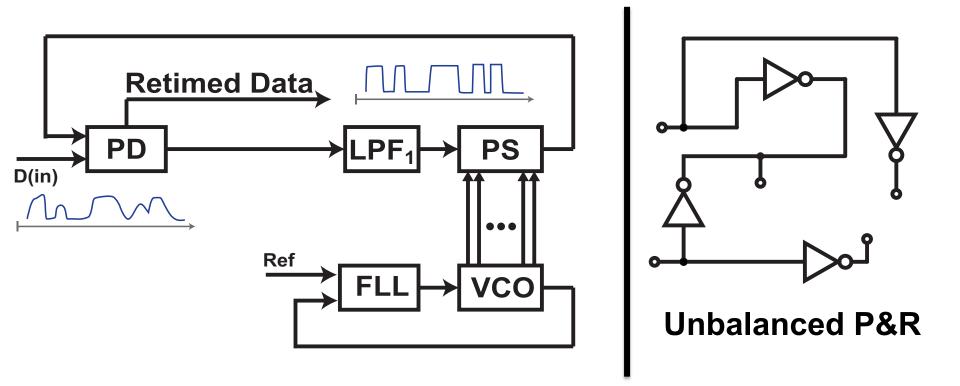

### **Conventional Architectures**

#### A new analog-circuit architecture is required, which tolerates layout impairment/uncertainty.

[M. Loh, e*t. al*., VLSI 2010] [H. Pan, e*t. al*., ISSCC 2011]

## **Conventional Architectures**

Architecture for synthesis must be minimally affected by layout variations.

| Topology         | PLL-CDR | DLL-CDR  | PI-CDR   | IL-CDR |

|------------------|---------|----------|----------|--------|

| Jitter Peaking   | Yes     | Yes*     | No       | No     |

| Locking Time     | Slow    | Moderate | Moderate | Fast   |

| Frequency Range  | Wide    | Wide     | Limited  | Wide   |

| Capture Range    | Wide    | Limited  | Limited  | Wide   |

| Synthesizability | No*     | No*      | No*      | Yes    |

#### **IL-CDR** is a viable candidate for synthesis

\*[Edward Lee, et. al., JSSC 2003]

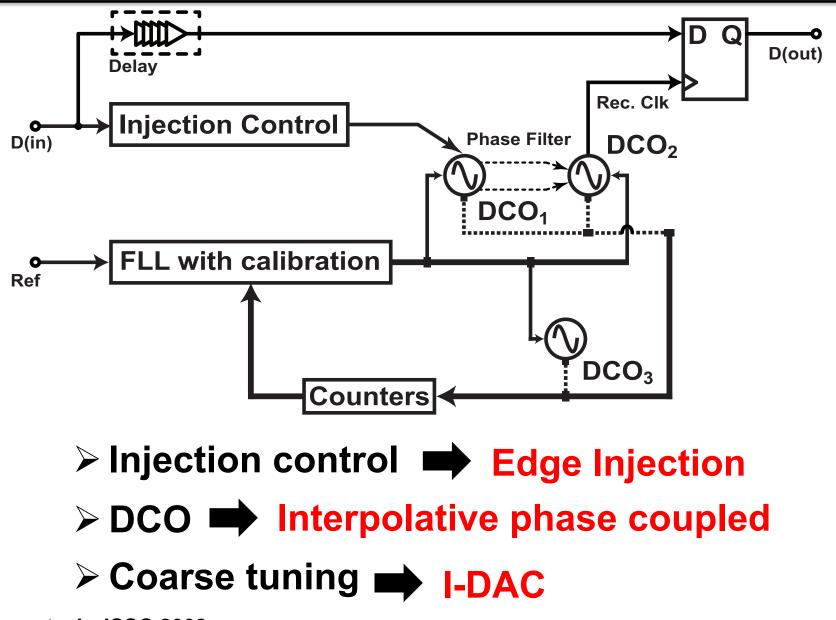

### **Architecture for Synthesis**

[J. Lee, et. al., JSSC 2008

## Outline

- Motivation

- Architecture for Synthesis

## -Edge Injection

- -Interpolative Phase-Coupled DCO

- -Standard Cell I-DAC

- **–PVT Calibration**

- Measurement Results

- Summary

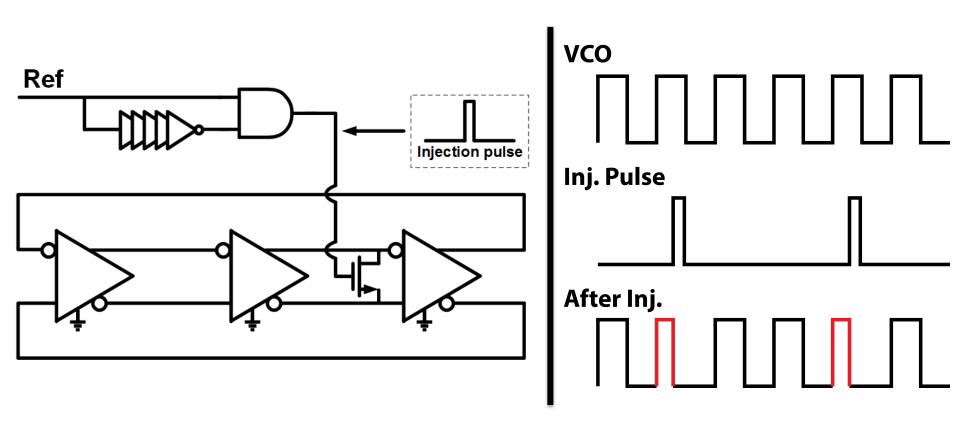

## **Conventional Pulse Injection**

Stringent timing constraints on inj. pulse width.

Reduced pulse width stress down-stream circuitry.

[Hiok, et. al., JSSC 2013]

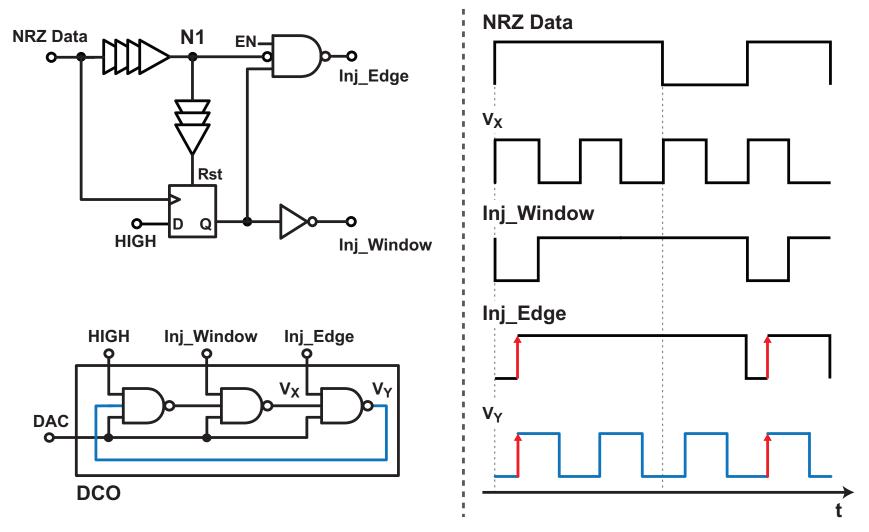

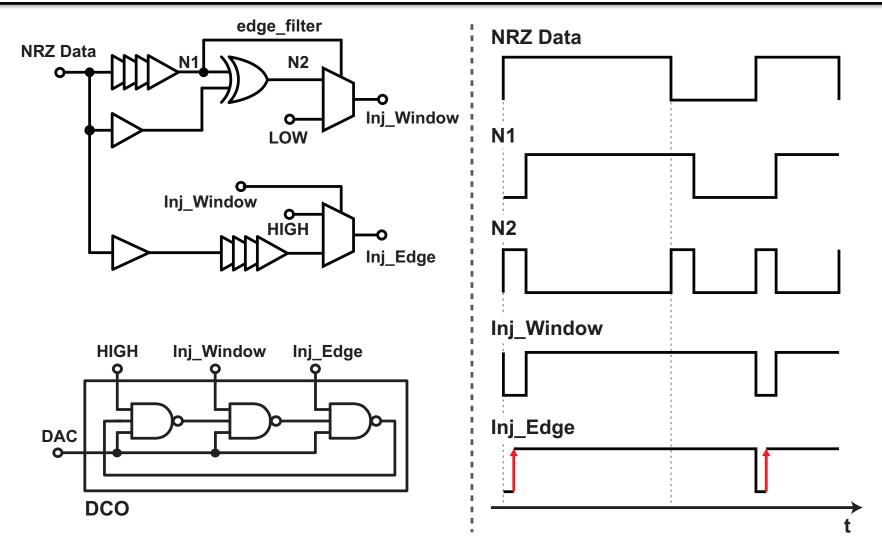

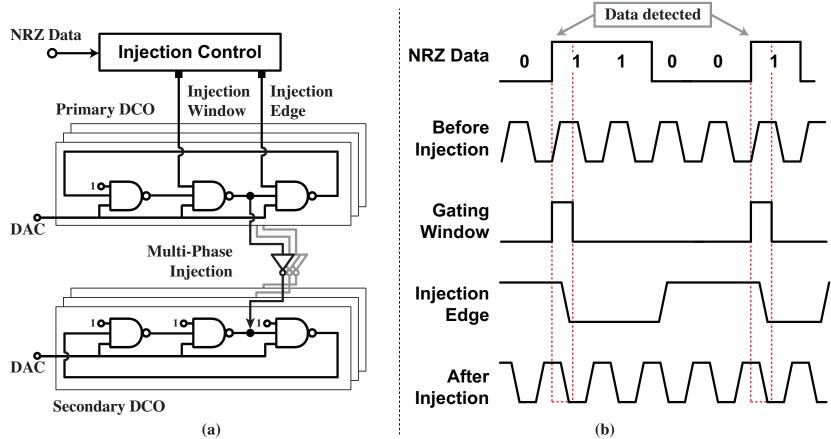

## **Edge Injection**

> Waveform distortion is eliminated.

[Deng, et. al., JSSC 2014]

## Edge Injection Contd.

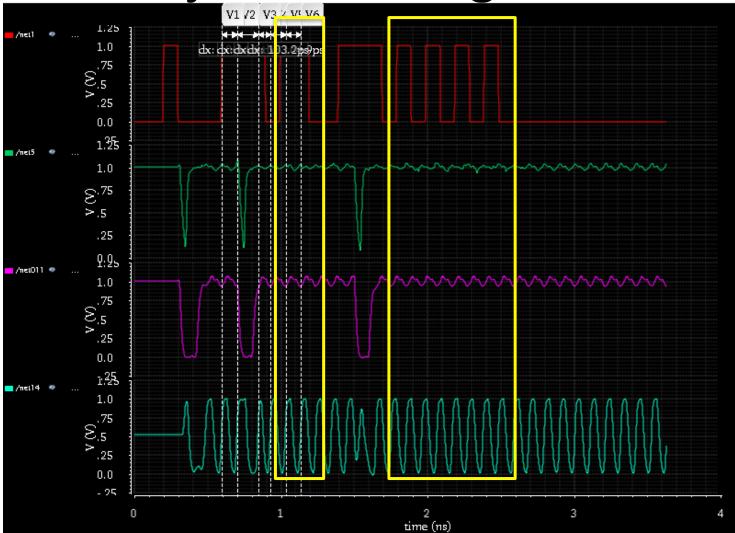

Improved circuitry for enhanced operation speed.

## Outline

- Motivation

- Architecture for Synthesis

- -Edge Injection

- -Interpolative Phase-Coupled DCO

- -Standard Cell I-DAC

- **–PVT Calibration**

- Measurement Results

- Summary

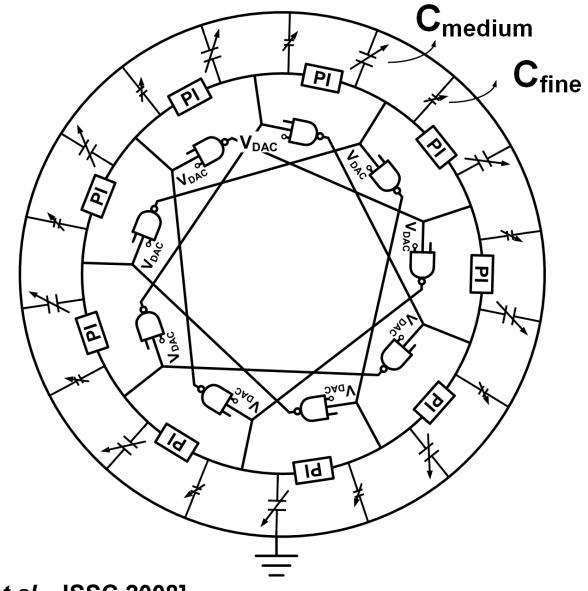

## **Block Diagram of DCO**

[A. Matsumoto, et al., JSSC 2008]

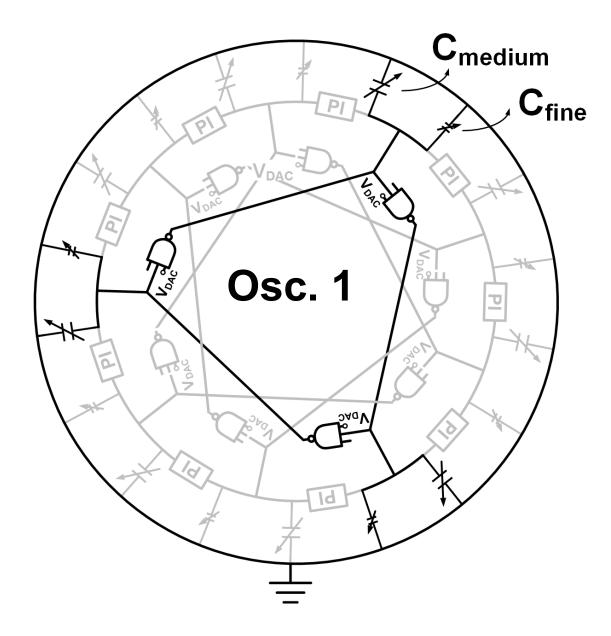

## **Block Diagram of Oscillator 1**

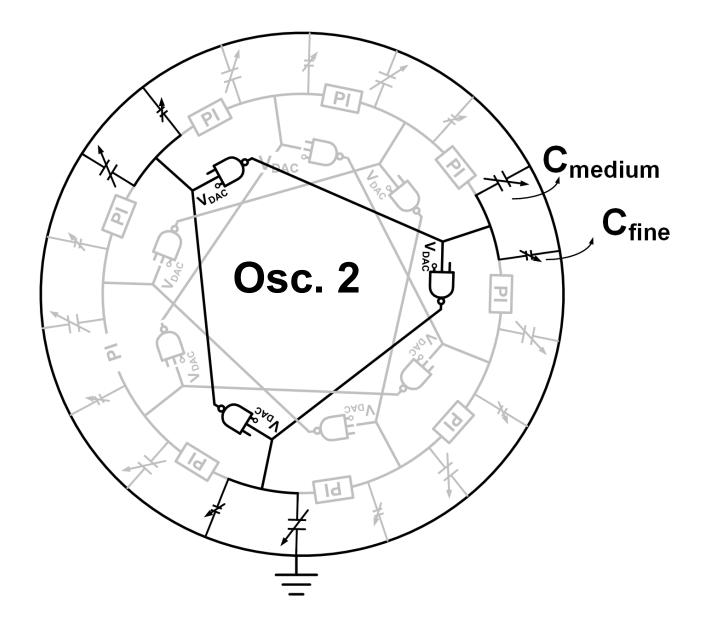

## **Block Diagram of Oscillator 2**

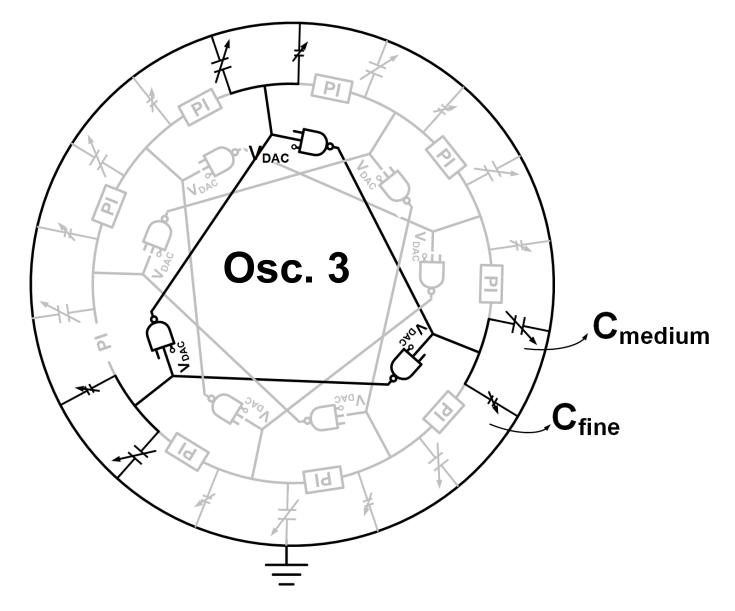

## **Block Diagram of Oscillator 3**

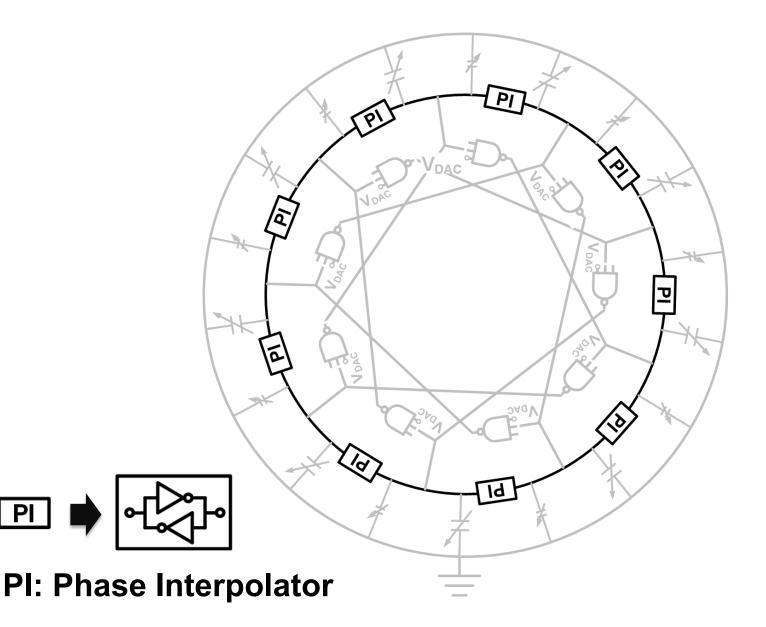

## **Interpolative Phase-coupled Ring**

## Outline

- Motivation

- Architecture for Synthesis

- -Edge Injection

- -Interpolative Phase-Coupled DCO

## -Standard Cell I-DAC

**–PVT Calibration**

- Measurement Results

- Summary

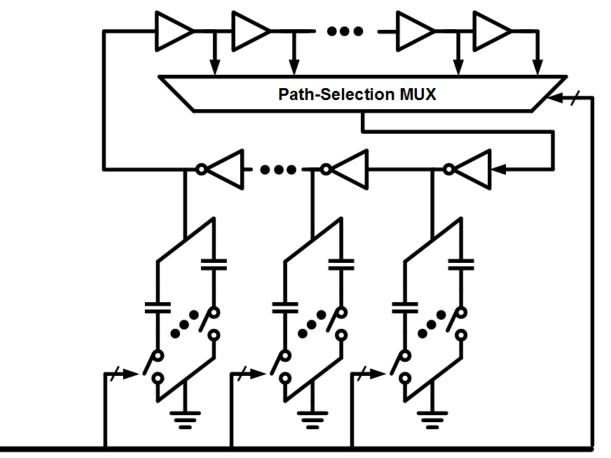

## **Conventional Coarse Tuning**

**Control code**

#### > Unequally loaded stages.

[D. Sheng, et al., TCAS II 2007]

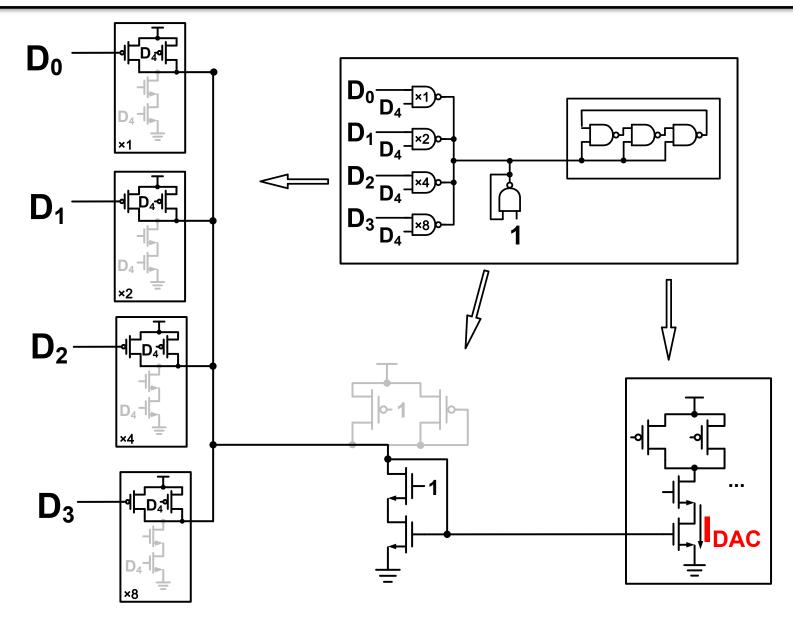

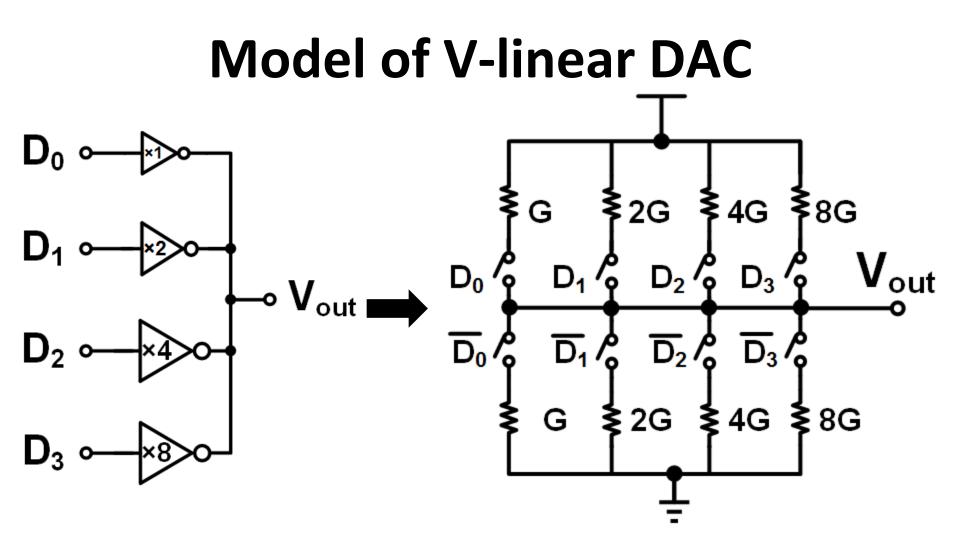

### **Coarse Tuning Using DAC**

Loading is equalized.

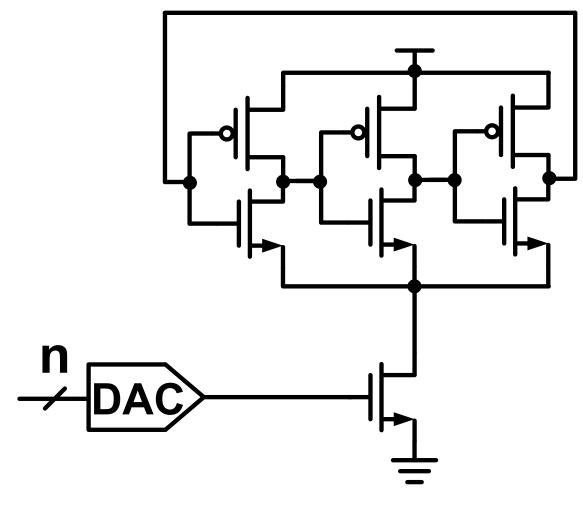

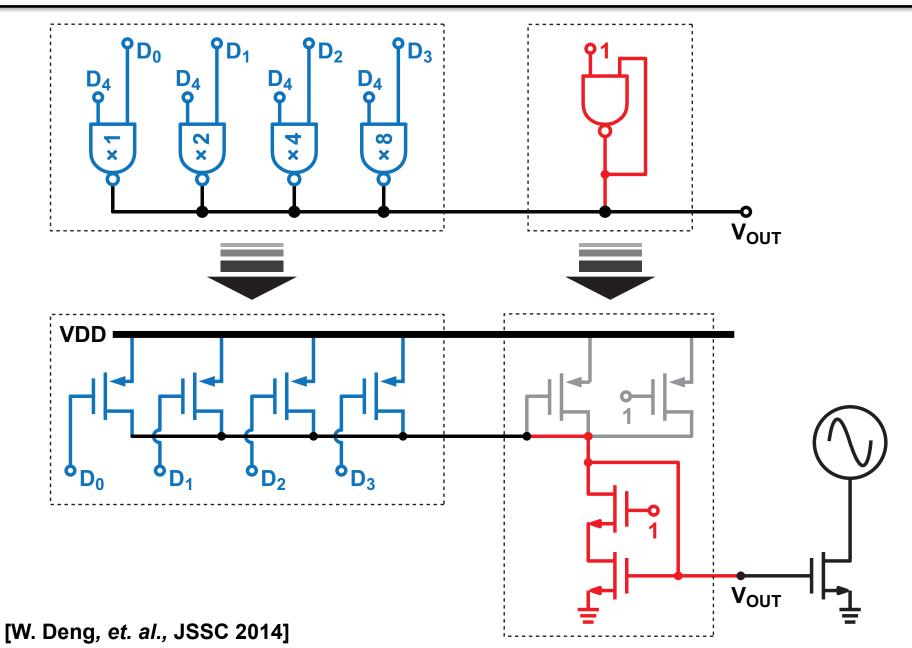

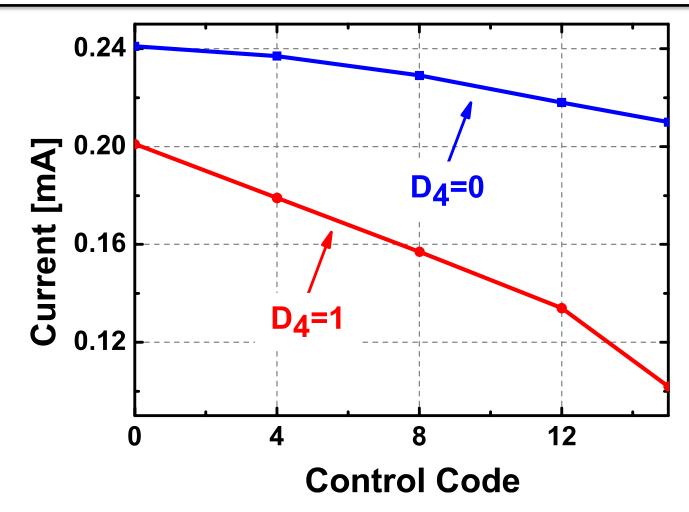

#### **I-Linear DAC**

#### I-Linear DAC Cont.

[W. Deng, et. al., JSSC 2014]

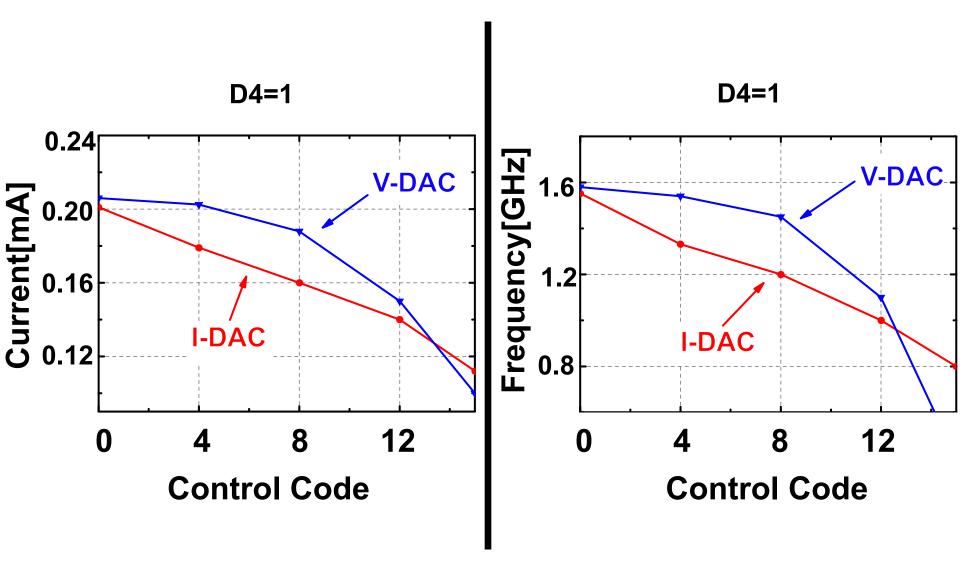

### **Simulation Results**

Approximately 2GHz tuning range is achieved in simulation using the I-linear DAC

## Outline

- Motivation

- Architecture for Synthesis

- -Edge Injection

- -Interpolative Phase-Coupled DCO

- -Standard Cell I-DAC

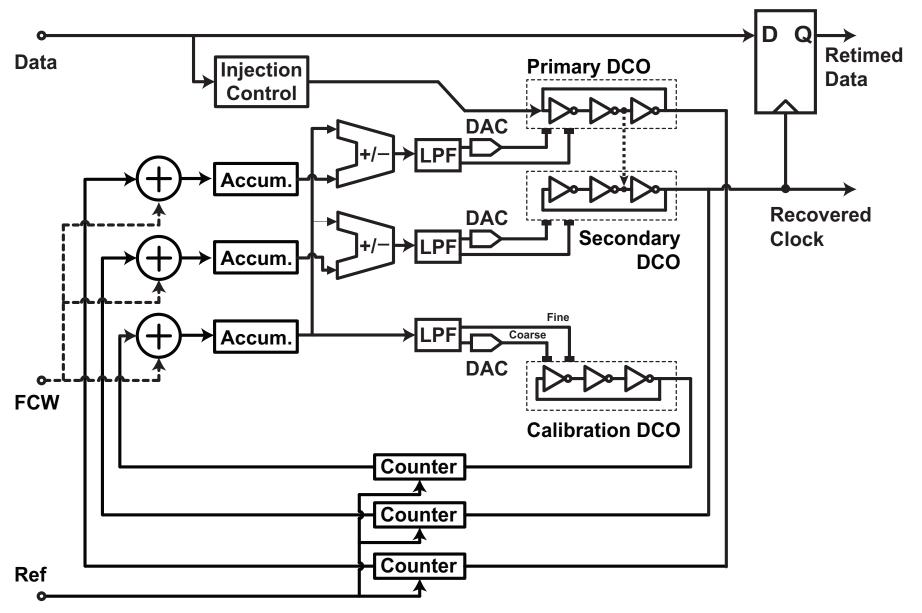

## **–PVT Calibration**

- Measurement Results

- Summary

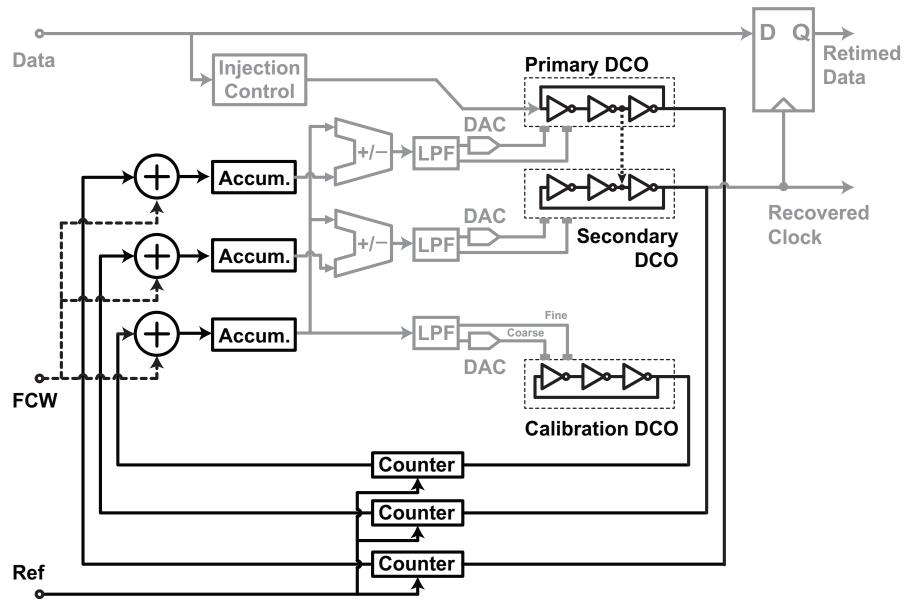

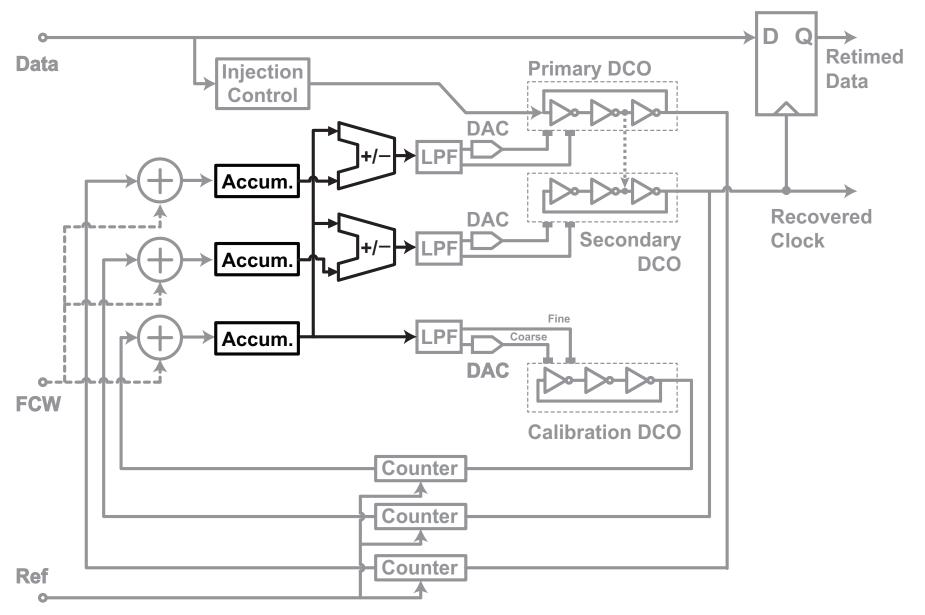

### **Complete Block Diagram**

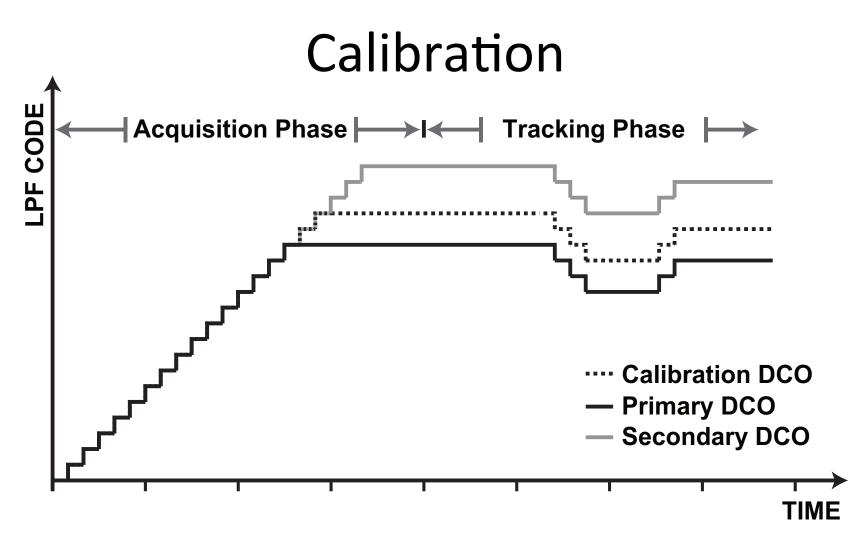

## **Calibration: Acquisition**

## **Calibration: Tracking**

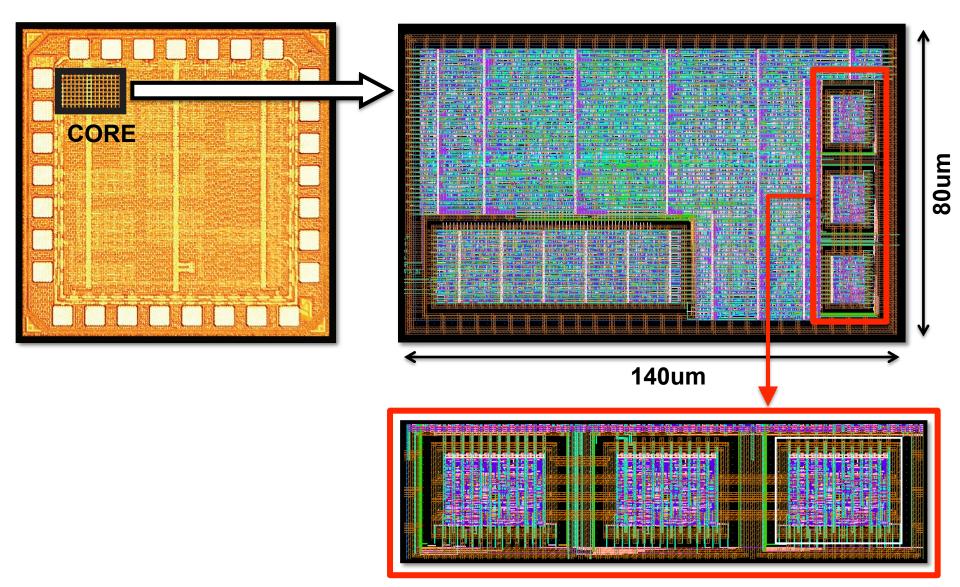

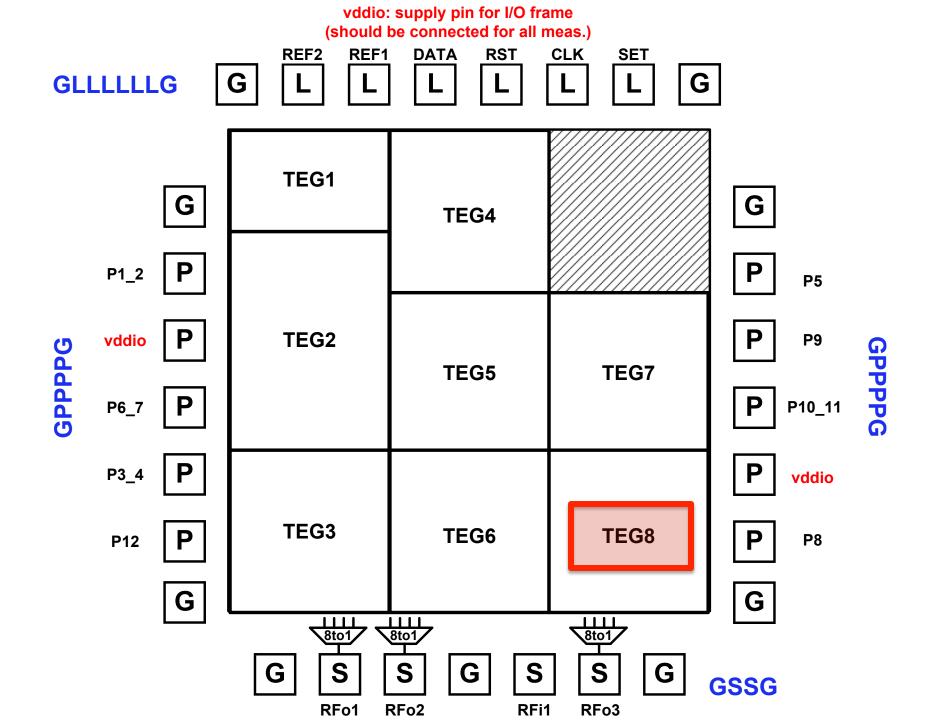

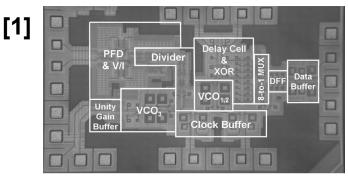

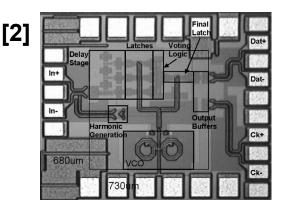

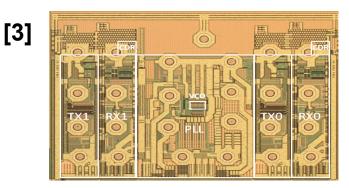

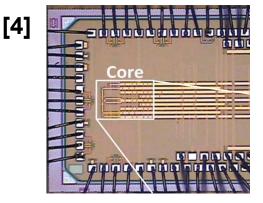

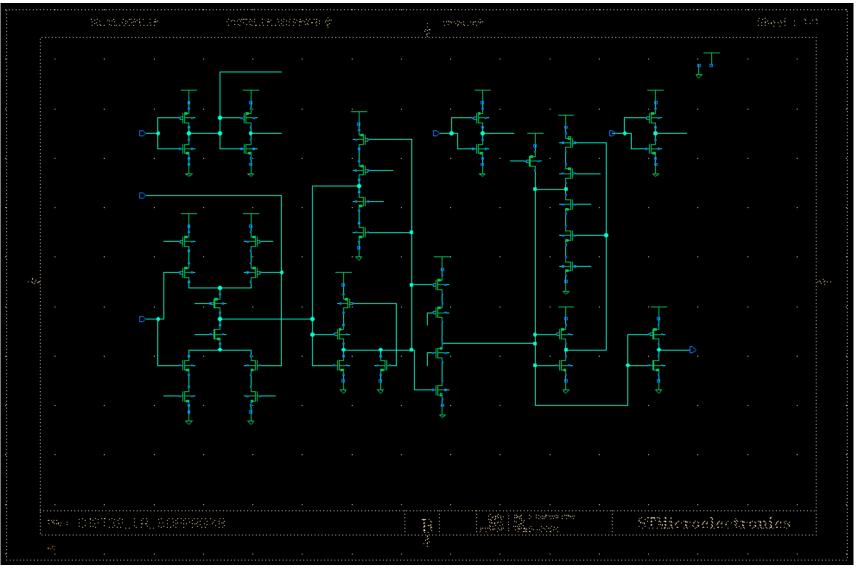

## **Chip micrograph and Layout**

#### **Identical DCOs**

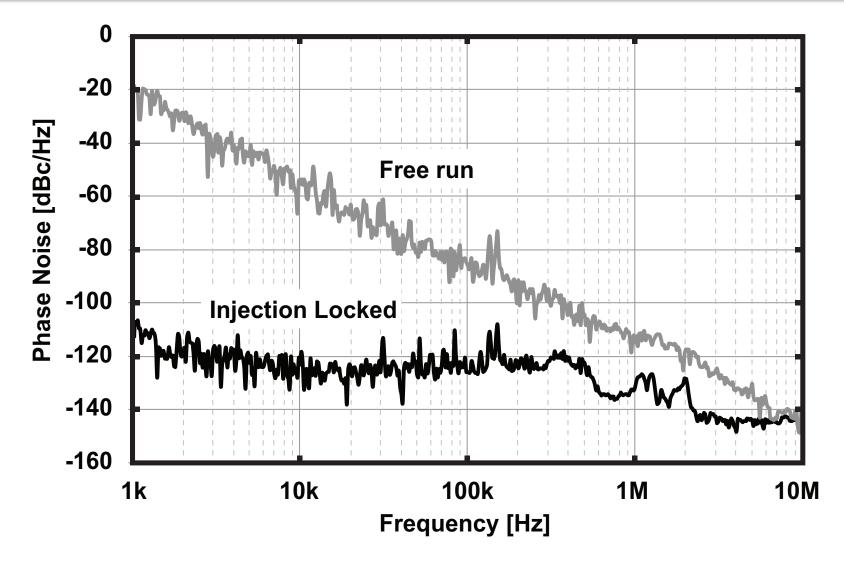

#### **Measurement Results**

Phase noise measured with SG as input.

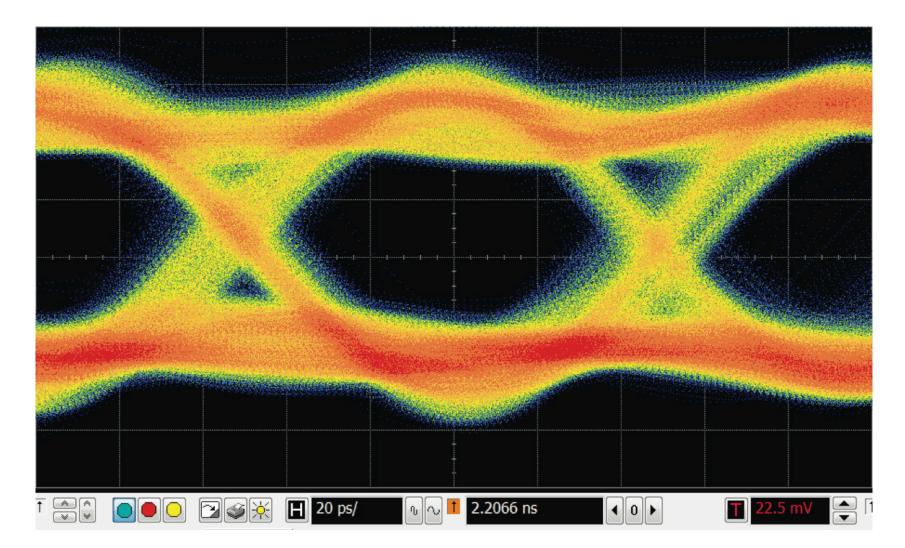

## **Eye Diagram**

#### Eye pattern measured at 10.05Gbps

## **Performance Comparison**

|                         | [1]        | [2]    | [3]     | [4]     | This    |

|-------------------------|------------|--------|---------|---------|---------|

| Technology              | 90nm       | 180nm  | 90nm    | 40nm    | 28nm    |

| Data Rate (Gb/s)        | 20         | 10     | 6       | 8       | 10      |

| Feature                 | Analog     | Analog | Digital | Digital | Digital |

| Locking Time (bits)     | N.A        | 32     | N.A.    | N.A.    | 1       |

| Power (mW)              | 102 (core) | 200    | 16.6    | 12      | 16      |

| Area (mm <sup>2</sup> ) | 0.96       | 3.4    | 0.234   | 0.0052  | 0.011   |

J. Lee, *et. al.*, JSSC 2008.

C.F Liang, *et. al.*, CICC 2006.

M. Loh, *et. al.*, VLSI 2010.

H. Pan, *et. al.*, ISSCC 2011.

## Conclusion

- Fully-synthesizable CDR is presented.

- Co-synthesis with digital core is possible.

- Saves design time and cost.

- Challenges arising from limited control over the layout is solved at architecture level.

- Edge Injection.

- Interpolative phase-coupled DCO.

- I-DAC.

- PVT calibration.

## APPENDIX

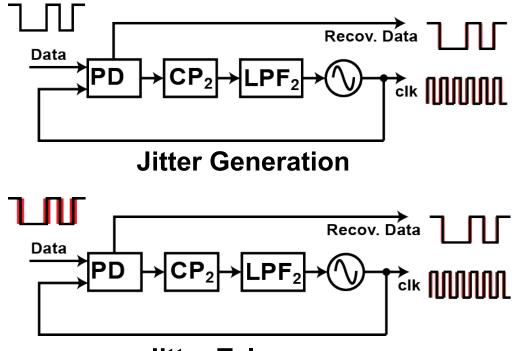

#### **Performance Metrics**

- Jitter Generation.

- Jitter Tolerance.

- Jitter Transfer.

- Acquisition Time.

- Capture Range.

**Jitter Tolerance**

## Why Fully-Synthesizable.

#### **Analog Implementations**

800umx1200um [90nm] 20Gbps

730umx680um [SiGe] 10.3Gbps

[1] Jri Lee, e*t. al.,* JSSC 2008 [2] Jing-Hong, e*t. al.,* CICC 2005

#### **Digital Implementations**

72umx72um [40nm] 8Gbps

460umx330um [90nm] 3x9Gbps

[3] Matthew Loh, *et. al.*, JSSC 2012[4] Hui Pan, *et. al.*, ISSCC 2011

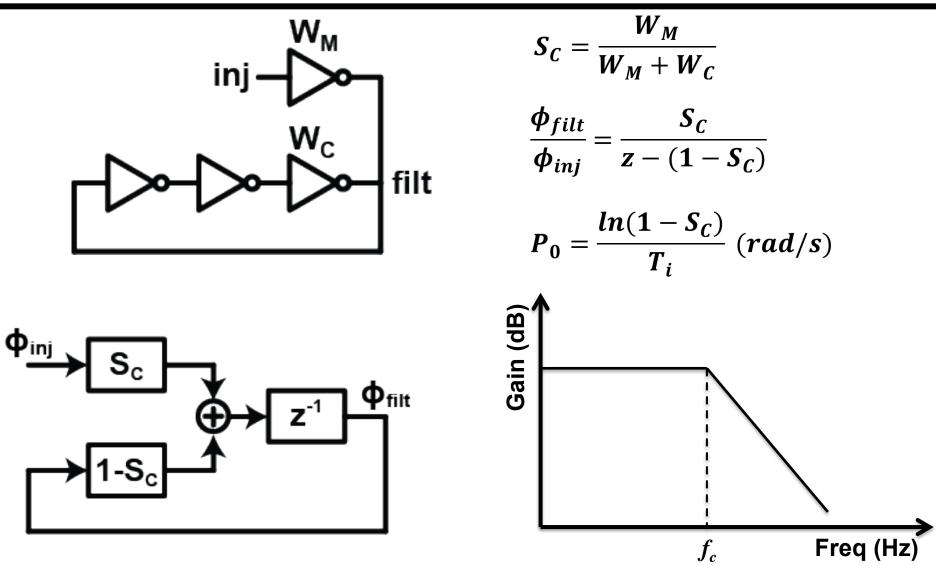

#### **Phase Filtering**

Hiok et. al, 2003 JSSC

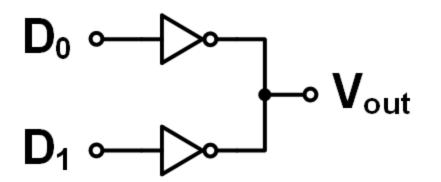

#### Simple Voltage-output DAC

$$D_0 \longrightarrow V_{out} \qquad \begin{array}{c} D_0 = 0 & V_{out} = 1V \\ D_0 = 1 & V_{out} = 0V \end{array}$$

How to obtain a I-linear DAC?

#### **V-DAC VS I-DAC**

#### **Injection Using DFF**

Transient Response

## 2:1 MUX [ST 28nm]

|      | - CONTROLLES ADDRESS - CO               |                                                                                      |                                       |

|------|-----------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|

|      |                                         |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

|      | · · · · · · · · · · · · · · · · · · ·   | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

|      |                                         |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

|      | ····                                    |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

|      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | 50                                                                                   |                                       |

|      |                                         | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

|      |                                         |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

| 08 D |                                         | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

|      | gradi •                                 |                                                                                      |                                       |

|      |                                         |                                                                                      |                                       |

|      | · · · · · · · · · · · · · · · · · · ·   |                                                                                      |                                       |

|      | · · · · · · · · · · · · · · · · · · ·   |                                                                                      |                                       |

|      |                                         | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

|      | sn2                                     | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

| 01   |                                         | · · · · · · · · · · · · · · · · · · ·                                                |                                       |

|      | gradi •                                 |                                                                                      |                                       |

|      |                                         | 50                                                                                   |                                       |

|      |                                         | <u></u>                                                                              |                                       |

|      |                                         |                                                                                      |                                       |

|      |                                         | este i Elefa e degli > Marketti Settel<br>Hava e degli<br>Alefani i Marketti i Sette | Whitercelectronics                    |

|      | อาณาสีนารรถสารสารสีนารรถสารสนับสุด<br>  |                                                                                      |                                       |

|      |                                         |                                                                                      | · · · · · · · · · · · · · · · · · · · |

## DFF [ST 28nm]

## **Phase Filtering**

> More jitter suppression by changing injection strength

Multi-phase injection for balanced phase and amplitude

Deng *et. al.,* 2003 JSSC. Hiok *et. al.,* 2003 JSSC.

Faster settling time compered to conventional calibration scheme.