# Proposal of layout-driven 1/2.8 size DAC design methodology

Tokyo Institute of Technology<sup>\*</sup> & JST, CREST<sup>+</sup> 菅原 光俊<sup>\*+</sup>、盛 健次<sup>\*+</sup>、李 承鍾<sup>\*</sup>、宮原 正也<sup>\*</sup>、松澤 昭<sup>\*</sup> M.Sugawara<sup>\*+</sup>,K.Mori<sup>\*+</sup>,SJ.Lee<sup>\*</sup>,M.Miyahara<sup>\*</sup>,A.Matsuzawa<sup>\*</sup> Nov 19, 2013

2

ΤΟΚΥΟ ΤΕCΗ **Pursuing Excellence**

Matsuzawa & Okada Lab.

## このDACの話をします

Proposal of layout-driven 1/2.8 size DAC design methodology

Nov 19, 2013

### Abstract

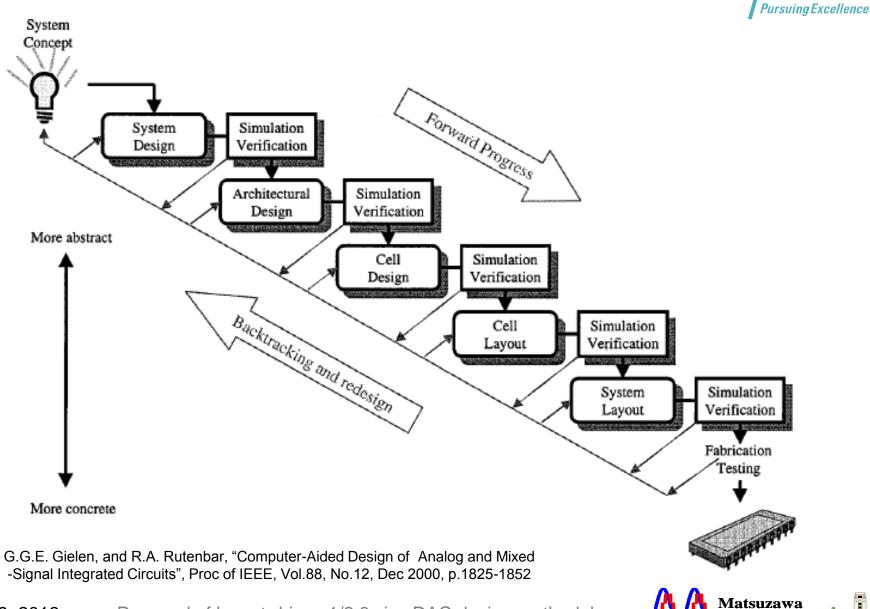

- Typcal D-to-A converter (DAC) design flow is hierarchical; architecture →circuit →layout design.

- We propose a layout-driven architecture and circuit design.

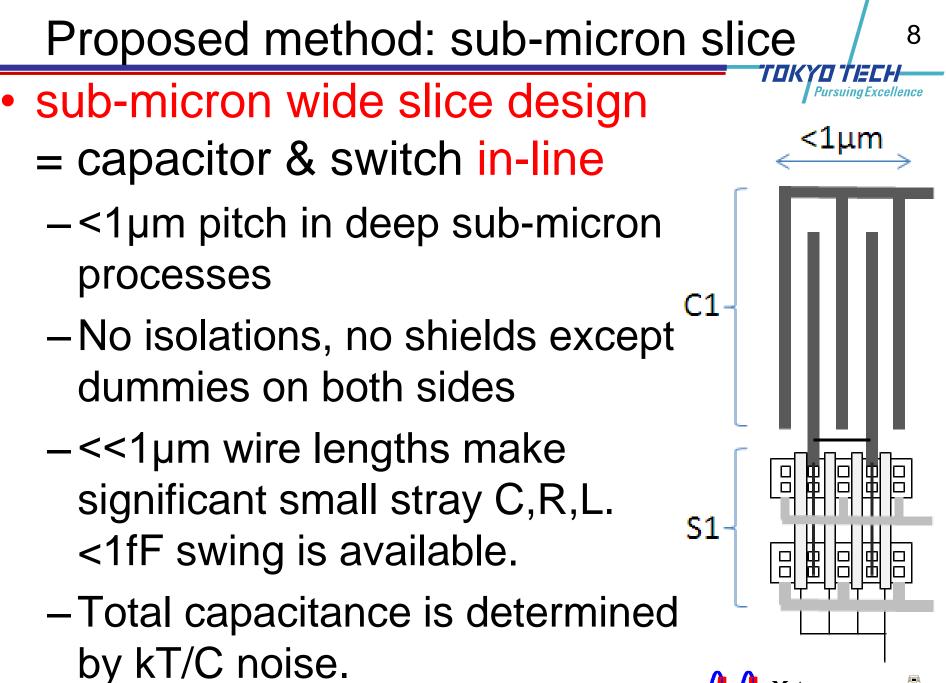

- We have successfully designed a sub-micron wide slice including unit capacitor & unit switches.

- It earns scalable & smaller parasitic C,R,L, then significant higher speeds and lower powers.

- Our new silicon samples of 12bit 1Gsps DAC in a SAR ADC has demonstrated only 1/2.8 area of our previous design, and they have demonstrated +20% higher speeds.

# Previous DAC design methodology

4

& Okada Lab.

## Previous DAC design example

Nov 19, 2013 Proposal of layout-driven 1/2.8 size DAC design methodology

& Okada Lab. 🎥 🏣

## Previous DAC design concerns

- Top down design methodologies

- Back-annotations & spice simulations can only guarantee final analog performances.

- Even though, layout designs have most constrains, less freedom.

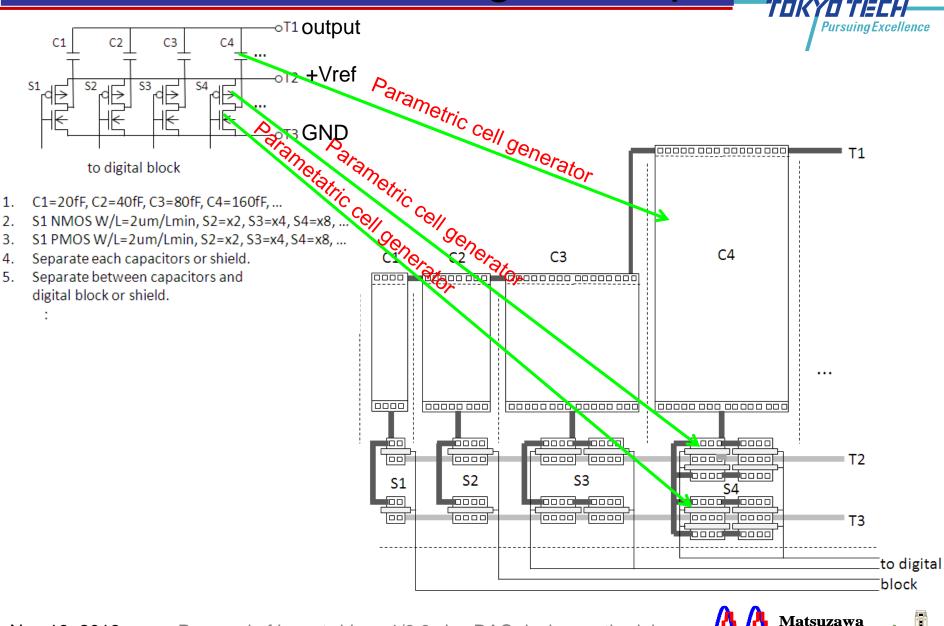

- Layout designers use parametric cell generators in layout tools. Cell size+ order (1~10~µm) designs.

- -Layout designers never initiate better architecture and circuit designs.

Nov 19, 2013 Proposal of layout-driven 1/2.8 size DAC design methodology

6

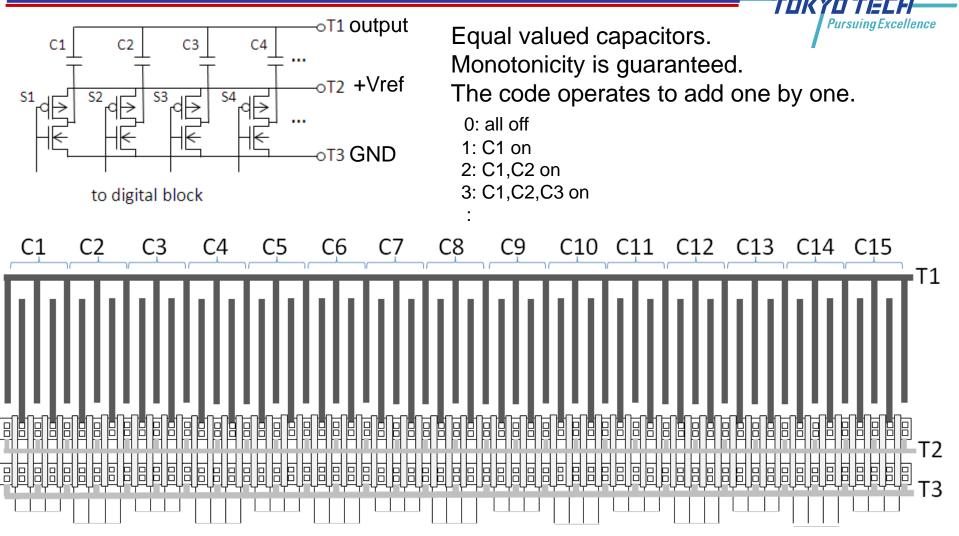

Proposed DAC design methodology

- Layout driven = Give layout 1<sup>st</sup> priority

- Consider smallest size, better matching, higher speed, etc. without cell border at layout point of view

- Common node T1 of capacitors instead of isolations and shields

- -Common source transistors w/o isolations

- -Use MOM capacitor (comb type)

- Less wires

Nov 19, 2013

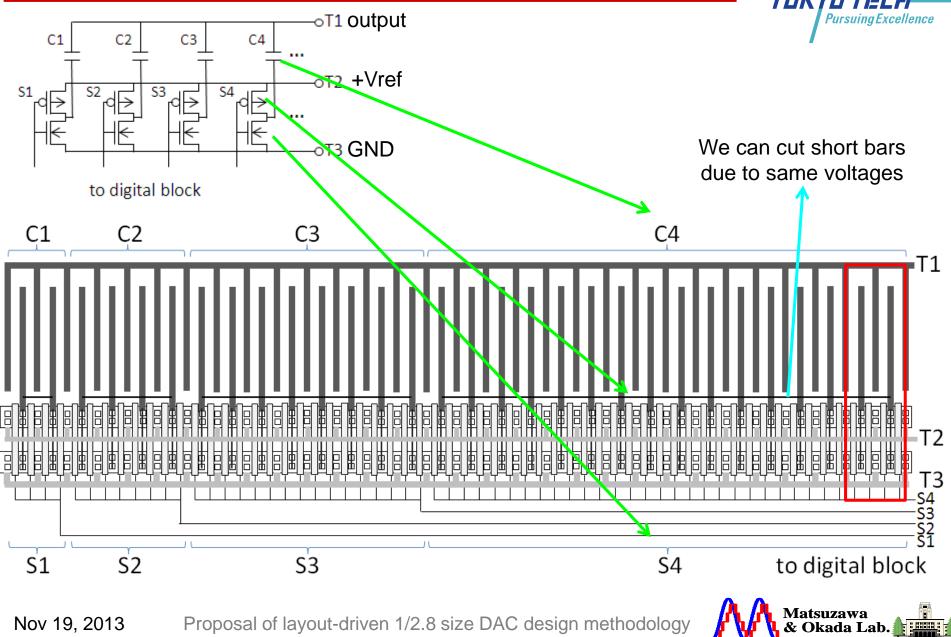

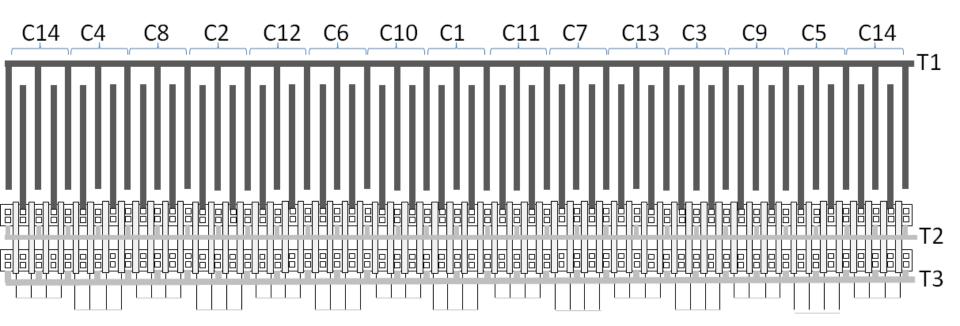

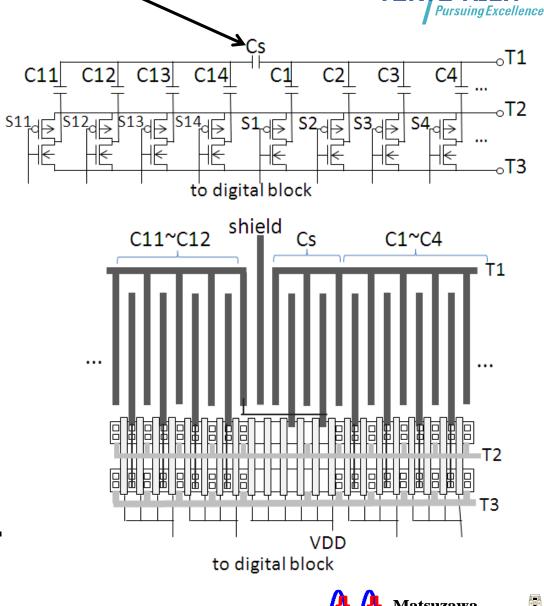

#### Proposed method: binary coded C-DAC 9

Proposal of layout-driven 1/2.8 size DAC design methodology Nov 19, 2013

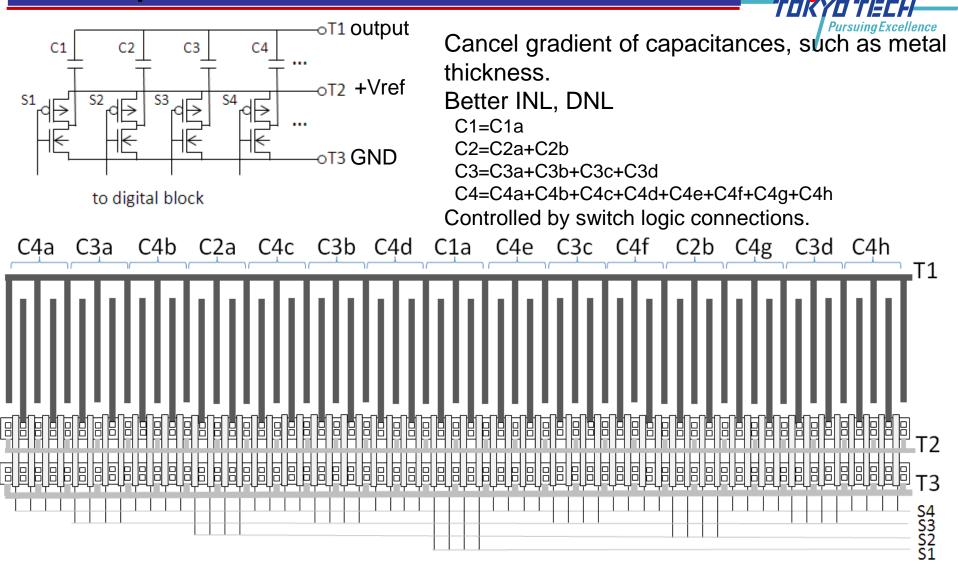

## Proposed method: scrambled binary

10

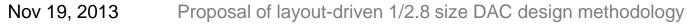

## Proposed method: thermometer coded <sup>11</sup>

#### Proposed method: scrambled thermometer

to digital block

Monotonicity is guaranteed. Better INL

Nov 19, 2013 Proposal of layout-driven 1/2.8 size DAC design methodology

12

Pursuina Excellence

#### Proposed method: scaling capacitor layout

- Scaling capacitor (2uint capacitance value) can be located in same slice except metal wires.

- It makes better match to keep same regularity.

13

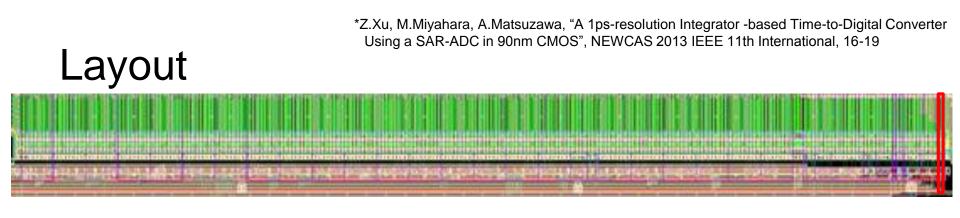

## Proposed method: experimental results 14

- Our silicon samples' experimental results

- 12bit DAC in SAR ADC

- DAC core size:  $0.0035mm^2=230\mu m \times 15\mu m$  (65nm) =1/2.8 of our previous design\* (90nm)

- Clock speed 1GHz. +20% higher then previous design\*

- Power consumption <2mW</p>

Nov 19, 2013 Proposal of layout-driven 1/2.8 size DAC design methodology

Pursuina Excellence

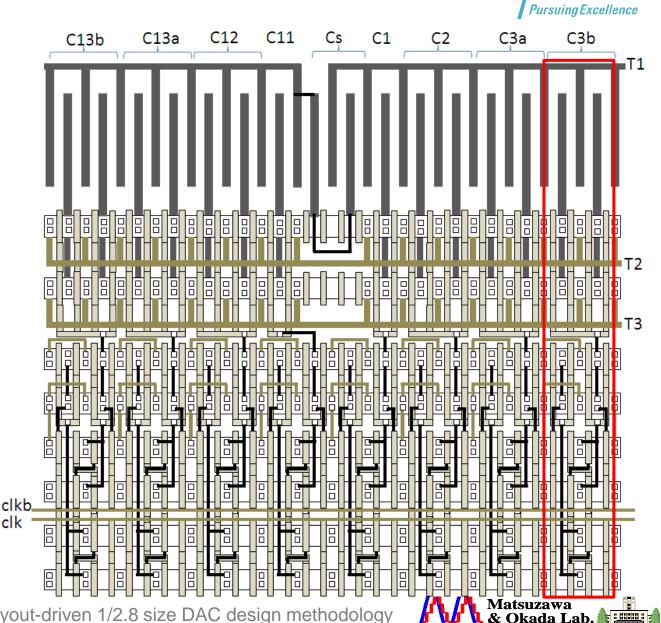

Proposed method: logic layout in slice

15

- Digital logic is also in sub-micron slice in-line, in addition to above

- D flip-flop (DFF) is located in-line by using 4 gates x 6 rows

- –<several µm metal wire length.</li>

Much smaller stray C,R,L than previous. →Higher speed

- Binary → thermometer coder can also be designed same size as DFF

- Any logic can be created into 4 gate per slice

Nov 19, 2013

## Proposed method: C+Sw+logic in slice

- Example

of

capacitor

+switches

+logic in

slice.

- Half

capacitor

in a slice

16

#### Proposed method: Scalable along processes

- Scalability along process nodes

- -Logic is scaled

- -MOS transistor switches are scaled

- Metal width and gap of MOM capacitors are scaled

- -Metal wire width is scaled

- Thermometer code arrows big capacitor mismatch (~50%error). Even smallest size capacitor can show enough performance

Hence, C-DAC by this method are scaled

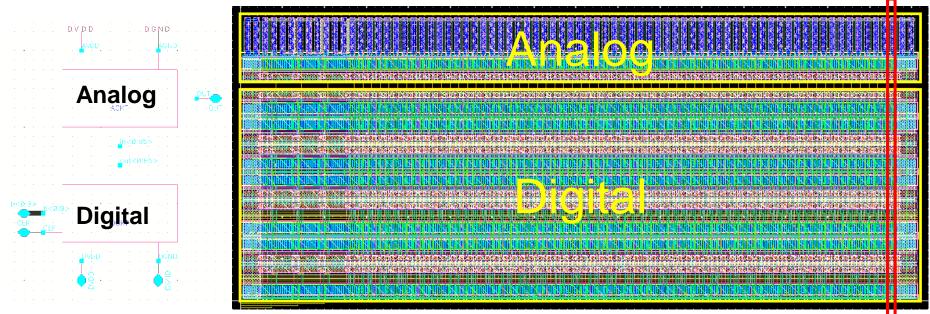

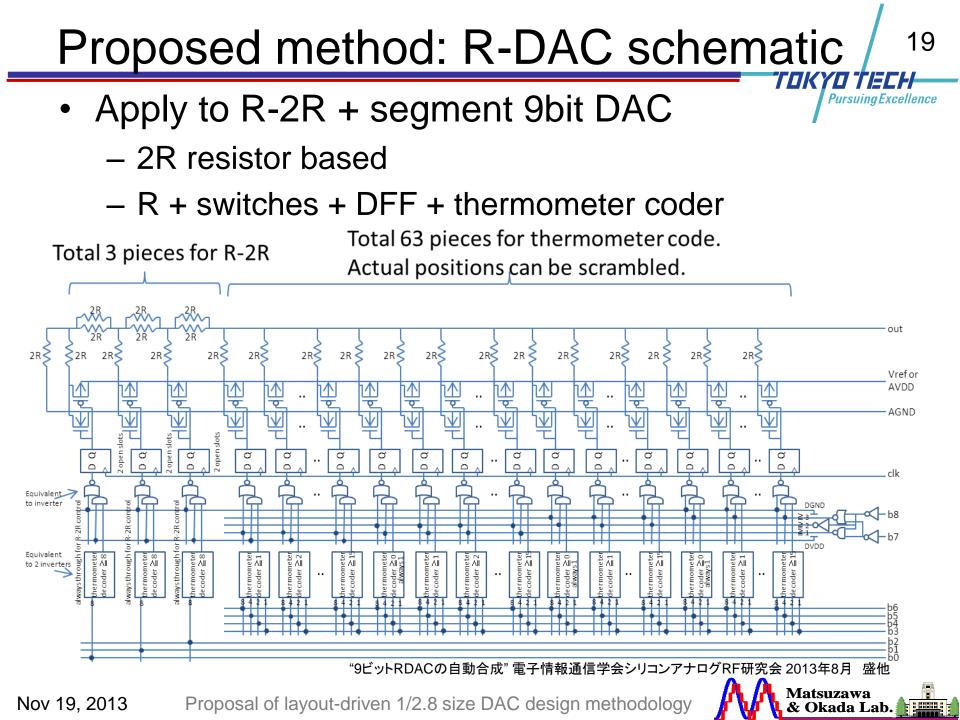

Proposed method: R-DAC layout

Apply to R-2R + segment 9bit DAC

#### -2R resistor based

–R + switches + DFF + thermometer coder

## **Automated layout**

"9ビットRDACの自動合成"電子情報通信学会シリコンアナログRF研究会 2013年8月 盛他

18

Pursuing Excellence

Matsuzawa

& Okada Lab.

## Conclusion

- We proposed layout driven architecture and circuit design

- -Give layout 1<sup>st</sup> priority

- Proposed sub-micron wide slice design

- -Quite small size (e.i. 1/2.8)

- Known, quite small stray C,R,L

→higher speed, lower power, etc.

→<1fF switching is available.</li>

- Process scalable analog design