# Essence and Technology Direction of ADC Design

#### Akira Matsuzawa

#### **Tokyo Institute of Technology**

# Outline

- Overview of ADCs

- OpAmp based ADC design: Pipeline ADC

- Comparator based ADC design : SAR ADCs

- Flash ADCs

- Summary

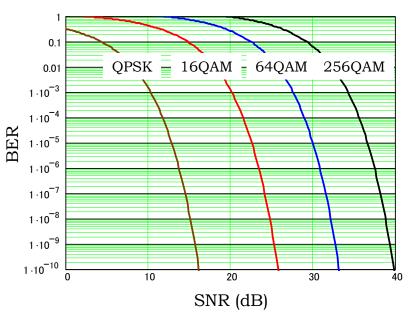

#### **ADC performance and data rate**

#### Data rate is proportional to the product of f<sub>s</sub> and N

**Conversion frequency is determined by signal bandwidth.**

$$C = BW \log_2 \left(1 + \frac{P_{\rm S}}{P_{\rm N}}\right)$$

SNR of ADC is

$BW < \frac{f_s}{2}$

$$\frac{\left. \frac{P_{\rm S}}{P_{\rm N}} \right|_{\rm ADC} = 1.5 \cdot 2^{2N}$$

Therefore

$$C \approx N f_s$$

f<sub>s</sub>: Sampling frequency N: Resolution

Higher data-rate can be realized by higher multi-level modulation. It result in increase of ADC resolution.

$D_{rate} \approx N f_s$

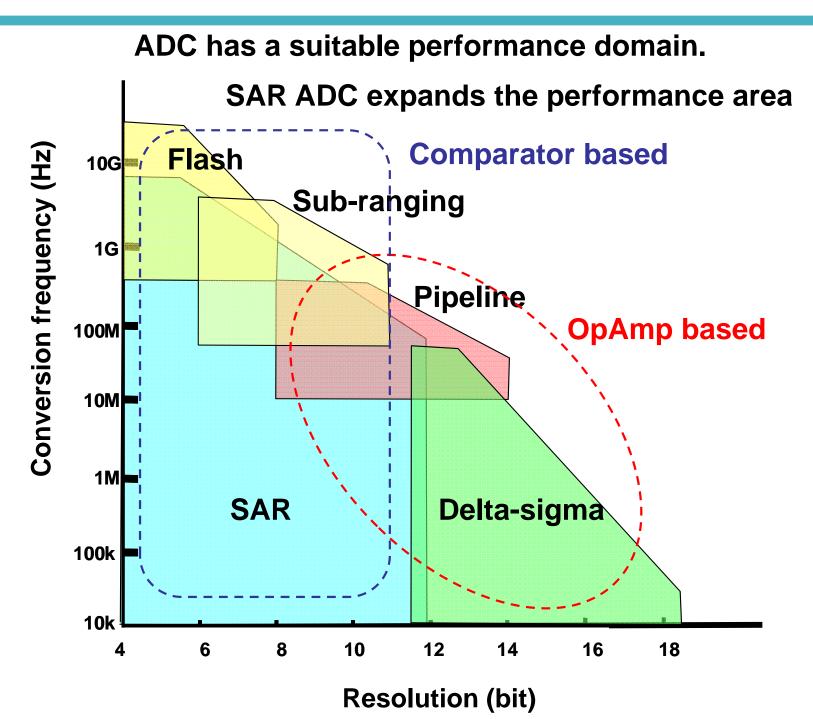

#### Performance and architectures of ADCs

#### Strategy of energy efficient ADC design

5

#### **Reducing static power**

Resistor DAC  $\rightarrow$  Capacitor DAC

**OpAmp based**  $\rightarrow$  **Dynamic comparator based**

**Reducing capacitance**

$\begin{array}{ll} E_d \approx CV_{DD}^2 & \text{ \# of CMP } \ \text{Flash} \rightarrow \text{SAR} \\ \\ \Delta V_T \propto \frac{1}{\sqrt{C_G}} & \text{TR size } & \text{Large TR} \rightarrow \text{Small TR with compensation} \\ \\ \overline{V_n} \propto \frac{1}{\sqrt{C}} & \text{Noise } & \text{Use complementally ckt.} \\ \\ \hline \text{Clock } & \text{Use self clocking} \end{array}$

#### Reducing voltage

Effective to digital gates

Use forward or adaptive body biasing

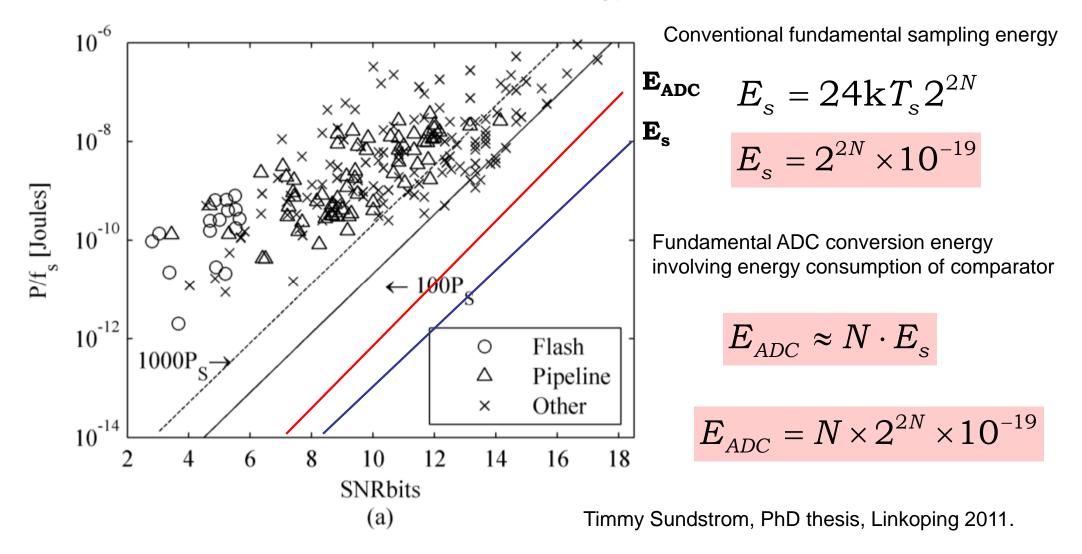

### **Fundamental Energy of sampling circuit** 6

Fundamental energy of sampling is often used.

However this neglects the power for comparison.

$E_s = 24 \mathrm{k} T 2^{2N}$

Signal

**Quantization noise power**

$V_{qn} = \frac{V_{FS}}{Q^N}$

**Quantization voltage**

$$P_{qn} = rac{V_{qn}^2}{12} = rac{V_{FS}^2}{12 \cdot 2^{2N}}$$

Noise balance

$$V_n^2 = P_{qn}$$

Capacitance

$$C = 12 \mathrm{k} T \frac{2^{2N}}{V_{FS}^2}$$

**Electrical energy=Thermal energy**

$$\frac{1}{2}CV_n^2 = \frac{1}{2}kT \quad \therefore \quad V_n^2 = \frac{kT}{C}$$

P<sub>d</sub> of sampling circuit

$$E_d = 2CV_{FS}^2 = 24kT2^{2N}$$

# **Energy consumption of ADC**

Consumed energy of ADC is mainly determined by the resolution. Energy of ADC is reaching 100x of the fundamental sampling energy, and 10x of the fundamental ADC energy consumption.

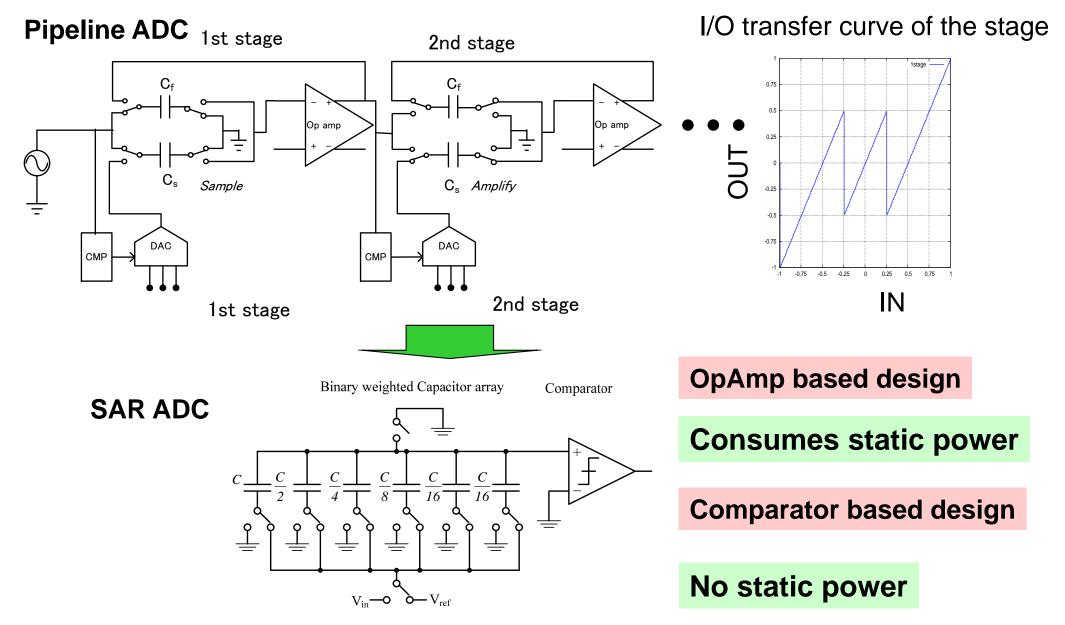

### **OpAmp based ADC design**

### **Pipeline ADC**

#### Mega-technology trend of ADCs

#### Major conversion scheme is now changing from pipeline to SAR.

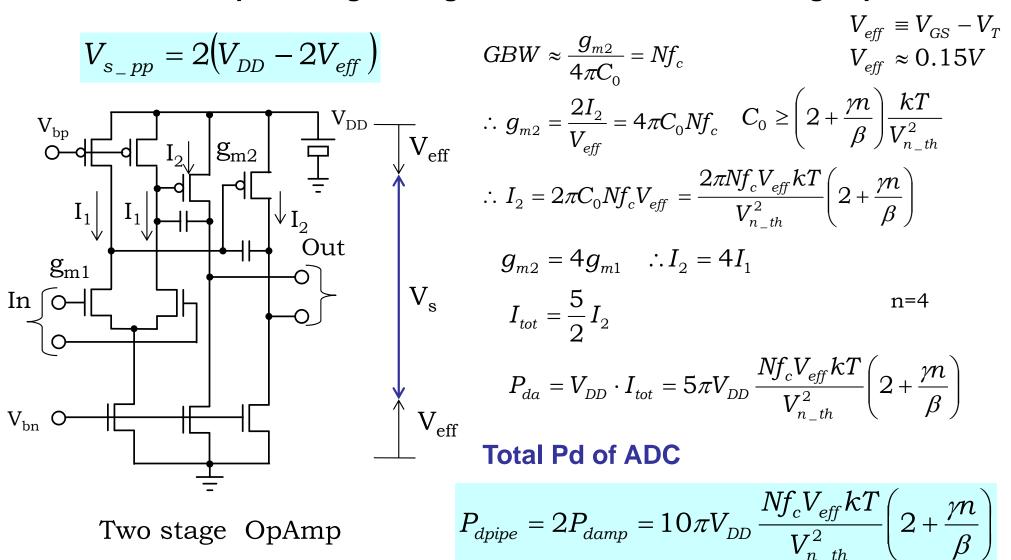

#### Low voltage OpAmp: Headroom and Pd 10

Two stage cascade OpAmp can realize low voltage operation. However, the output voltage swing becomes lower at low voltage operation.

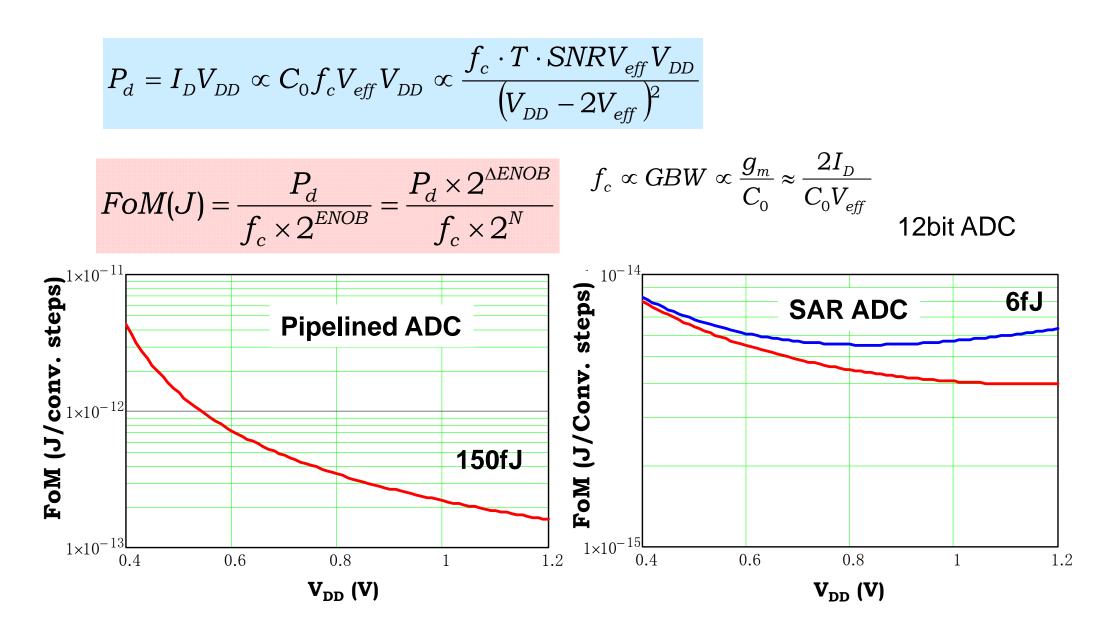

#### FoM vs. V<sub>DD</sub>

#### An OpAmp based ADC consumes large conversion energy

## **Comparator based ADC design**

: SAR ADC

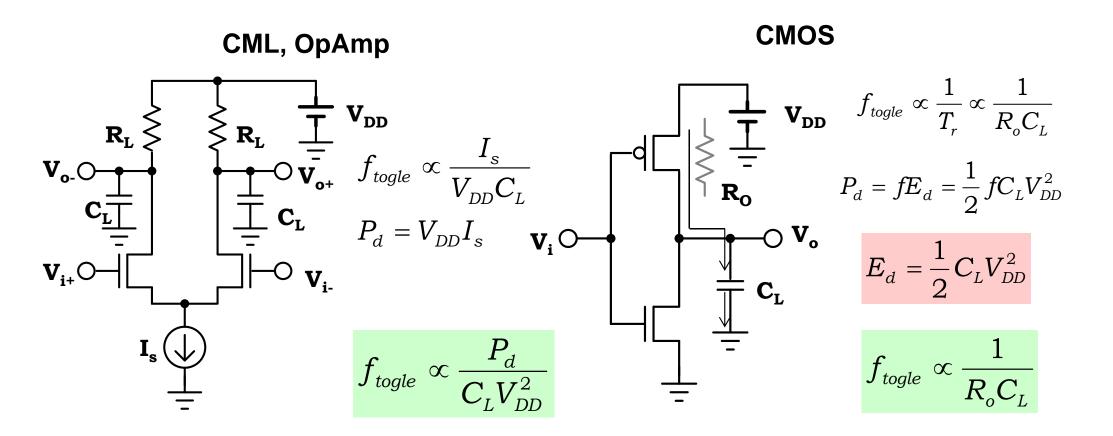

#### Basic idea for low energy analog design 13

Conventional analog circuit consumes larger energy. Dynamic circuits doesn't consume larger energy.

CMOS: Consumed energy is independent of the delay time.

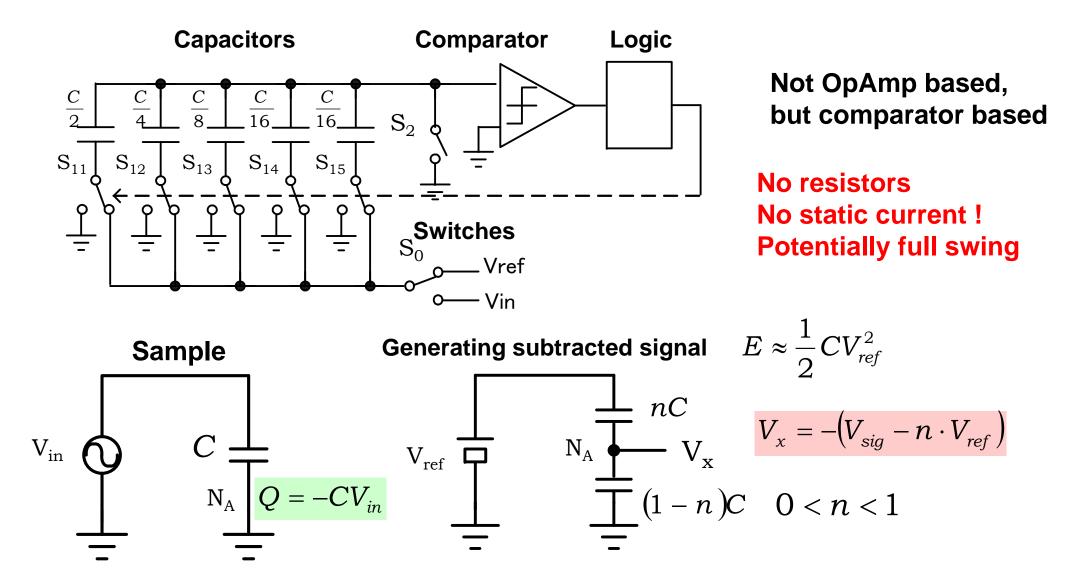

## SAR ADC

SAR can be designed to consume no static power.

SAR can realize larger signal swing compared with pipeline ADC.

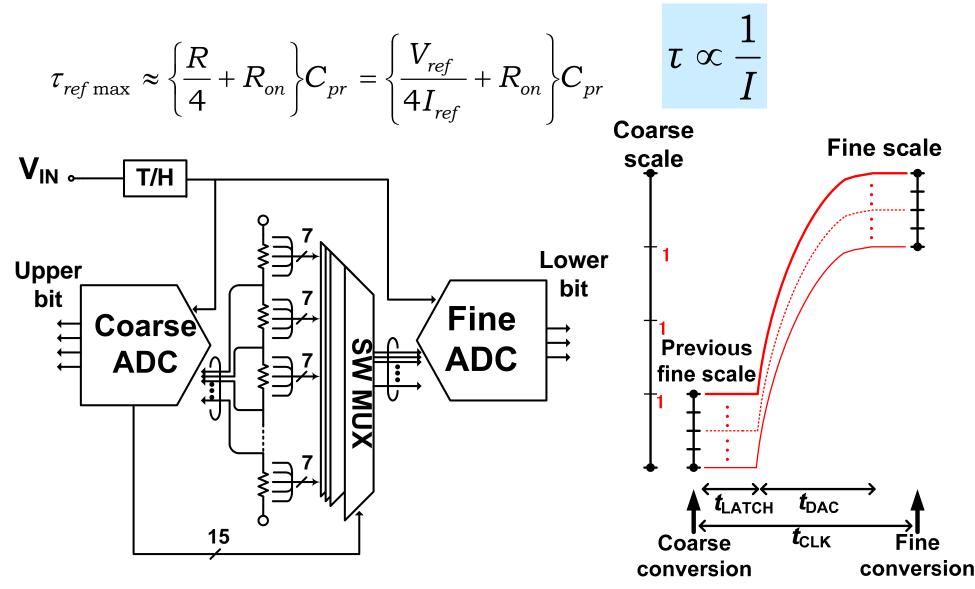

#### Issue of resistive DAC to generate V<sub>REF</sub> 15

Resistive DAC consumes static power and has a serious tradeoff between Pd and speed.

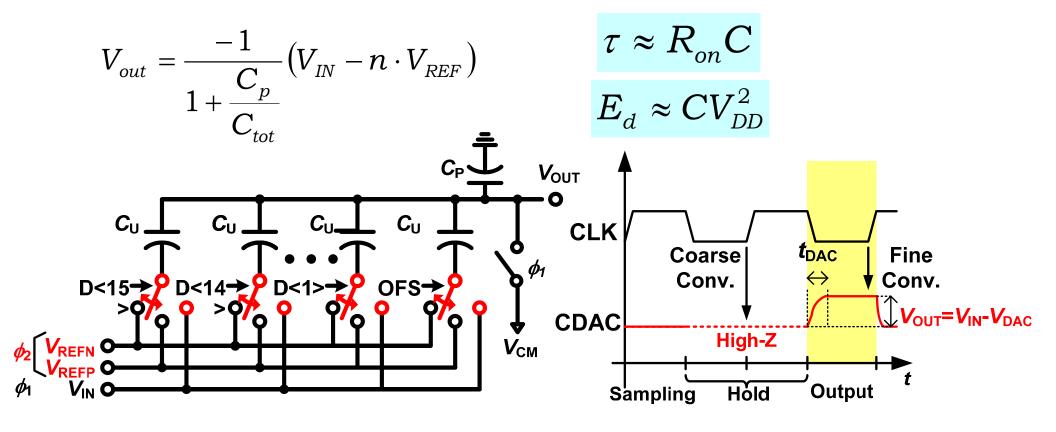

#### Advantage of capacitive DAC to generate V<sub>REF</sub> 16

Capacitor DAC doesn't consume static power and has no trade off between Pd and speed.

**Operating as S/H circuit**

- No static power consumption (360µW@1GHz)

- Smaller C<sub>u</sub> realize faster settling time (t<sub>DAC</sub>= 3.4 r<sub>on</sub>C<sub>U</sub> < 80ps @ r<sub>ON</sub> = 1kΩ, C<sub>U</sub>= 15fF)

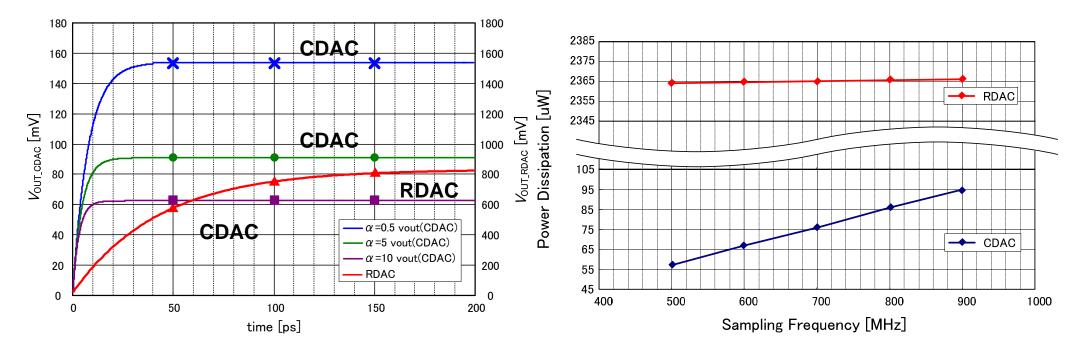

### Settling time and power

# CDAC realizes faster settling time to RDAC with low power consumption.

**Time response**

**Power dissipation**

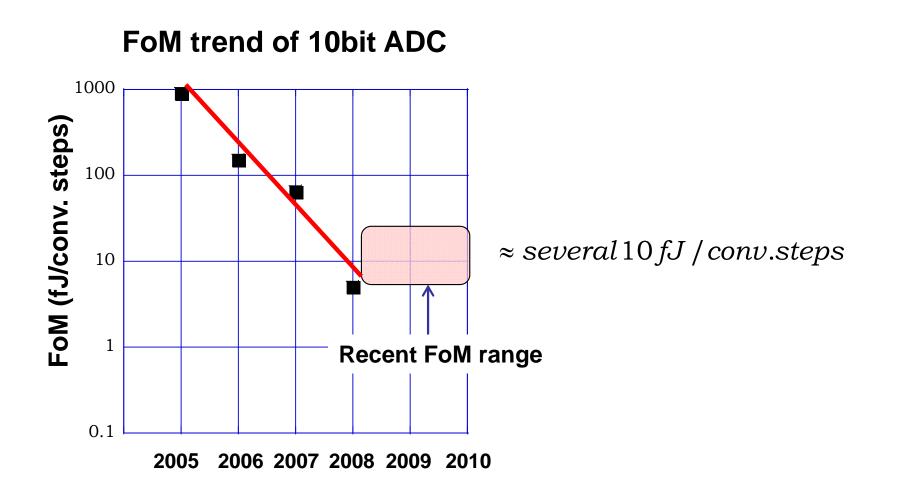

#### Performance overview of SAR ADCs

18

FoM has lowered rapidly due to the progress of SAR ADC.

1/200 during three years.

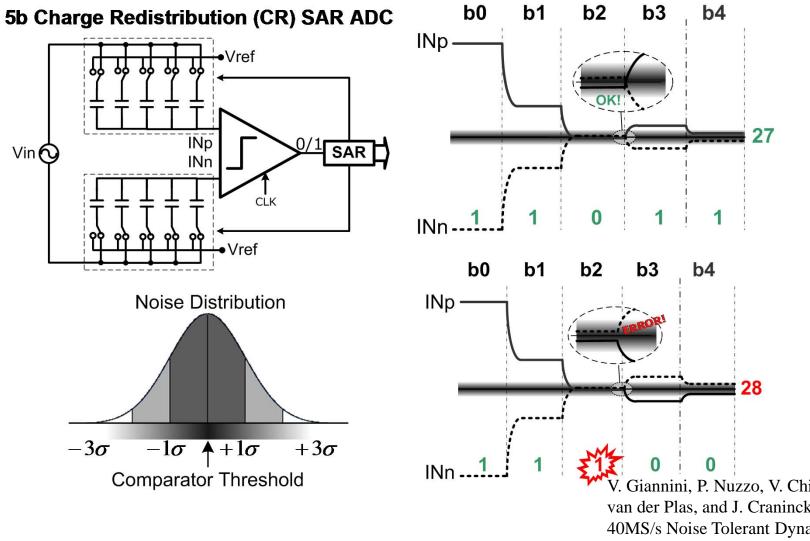

#### **Issue of comparator for SAR ADCs**

#### A comparator has noise and this results in conversion error.

V. Giannini, P. Nuzzo, V. Chironi, A. Baschirotto, G. van der Plas, and J. Craninckx, "An 820uW 9b 40MS/s Noise Tolerant Dynamic-SAR ADC in 90nm Digital CMOS," IEEE ISSCC 2008, Dig. of Tech. Papers, pp.238-239, Feb. 2008.

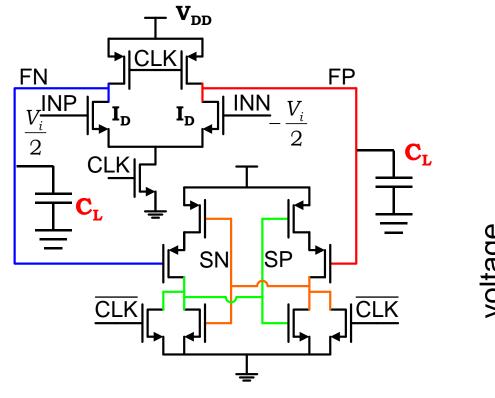

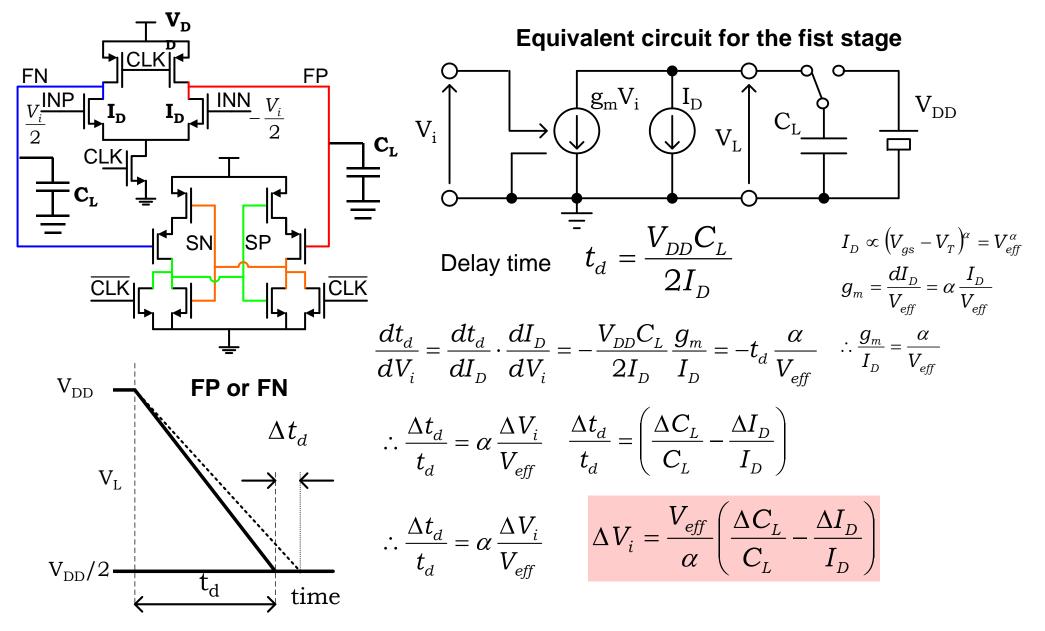

## **Dynamic comparator**

A dynamic comparator is widely used to reduce static power.

The difference in input voltages causes a difference in discharging speed.

D. Schinkel, E. Mensink, E. Klumperink, Ed Van Tuijl, B. Nauta,

"A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup-Hold Time," ISSCC Dig. of Tech. Papers, pp.314-315, Feb., 2007.

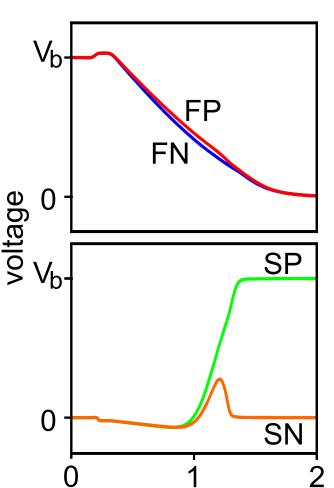

#### **Deriving noise equation**

A. Matsuzawa," IEEE 8th International Conference on ASIC(ASICON), pp. 218-221, Oct. 2009.

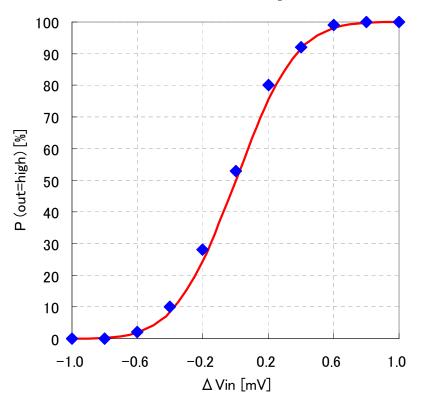

#### Match with noise simulation

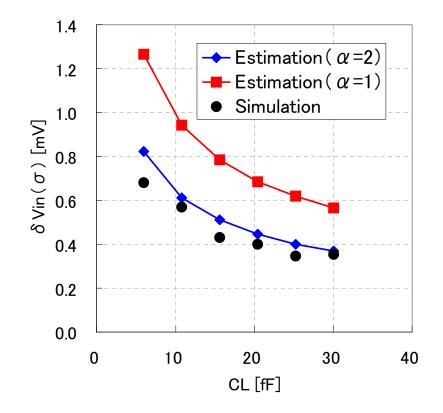

The derived equation has a good match with simulation.

$$\delta V_{in}^2 = \frac{4kTV_{eff}^2}{a^2 C_L V_{dd}^2} \left(a\gamma \frac{V_{dd}}{V_{eff}} + 1\right)$$

#### Noise in comparator

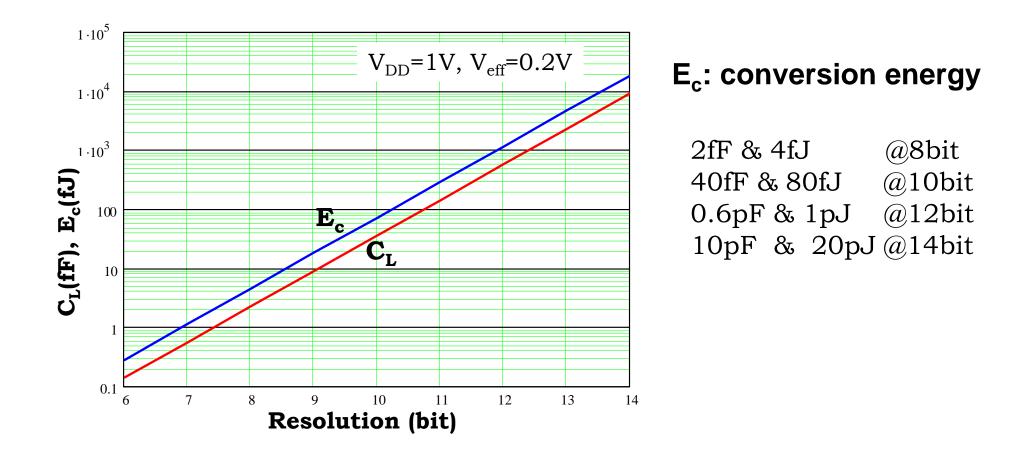

#### **Required capacitance and consumed Energy** 23

Node capacitances should be increased to realize higher ADC resolution. This results in increase of consumed energy of the dynamic comparator.

Flash ADC: $E_c$  determines the minimum FoMSAR ADC: $E_c$  cannot be neglected for higher resolution ADC

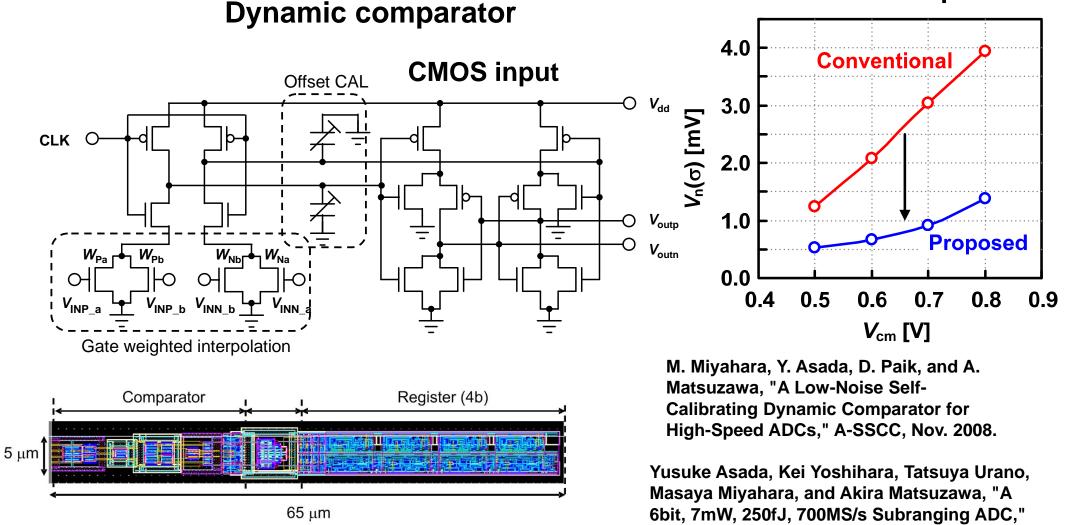

#### Noise improvement of dynamic comp. 24

Noise of comparator can be reduced by complementary ckt. and an optimization of the node capacitance.

Noise of comparator

A-SSCC, 5-3, pp. 141-144, Taiwan, Taipei, Nov.

90nm CMOS

2009.

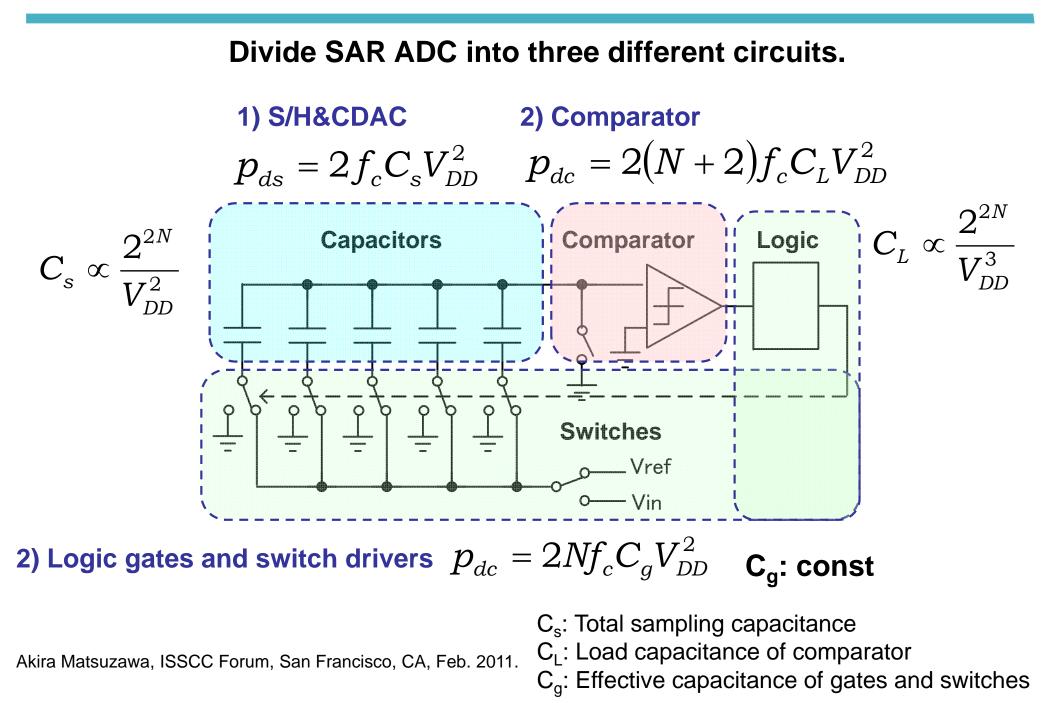

#### **P**<sub>d</sub> estimation of SAR ADC

#### Equations to estimate the ADC performance 26

Quantization

$$\overline{V_q^2} = \frac{1}{3} \left( \frac{V_{DD}}{2^N} \right)^2$$

Permitted thermal  $V_{n\_th}^2 = \left(2^{2\Delta ENOB} - 1\right)\overline{V_q^2}$  Thermal Noise of COMP.  $V_{n\_th}^2 = \frac{4kT}{C_L} \left(\gamma \frac{V_{DD}}{V_{eff}} + 1\right) \left(\frac{V_{eff}}{V_{DD}}\right)^2$ noise

San cap

### C, $P_d$ , and FoM vs. $V_{DD}$

$C_s$  and  $C_L$  increase with reducing  $V_{DD}$ , since the quantization voltage decreases with reducing  $V_{DD}$ .

$P_d$  of S/H is constant for  $V_{DD}$ , however  $P_d$  of comparator increases with reducing  $V_{DD}$ .  $P_d$  of logic gate decreases rapidly with reducing  $V_{DD}$ .  $P_{dc} \propto rac{1}{V_{DD}} \quad P_{dg} \propto V_{DD}^2$  $1 \times 10^{-11}$ 0.01 $C_s \propto \overline{V_{DD}^2}$ Comp **C**<sub>s</sub> Logic (F) 1×10<sup>-</sup>  $P_d$  (W)  $\mathbf{\dot{v}}_{1\times10^{-12}}$ C\_=0.3p] **C**<sub>L</sub> S/H 1×10<sup>-</sup> = const.  $C_{a}=0.1 pF$  $C_{I} \propto \frac{1}{173}$ תת  $1 \times 10^{-13}$ 1×10<sup>-</sup> 0.4 0.6 0.8 0.4 0.8 1.20.6 1 1.2 $^{Vd}$   $\boldsymbol{V_{DD}}$  (V)  $\mathbf{V}_{\mathrm{DD}}$  (V)

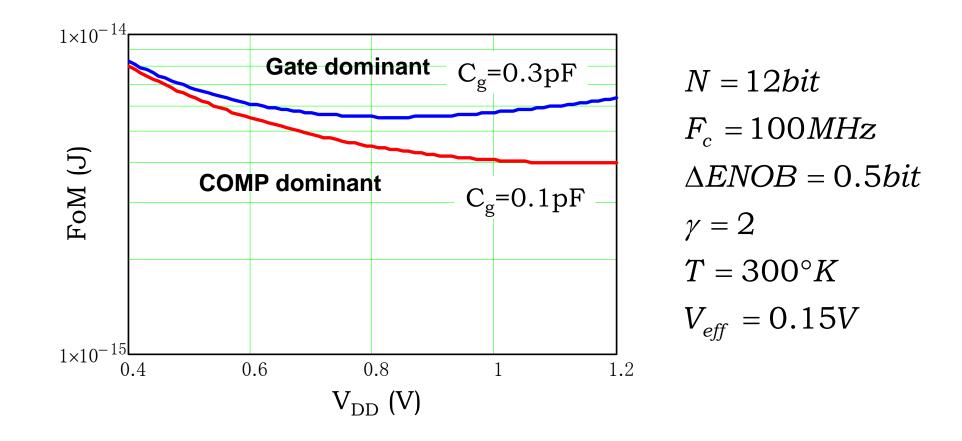

# FoM vs. $V_{DD}$

FoM can be lowered by reducing  $V_{DD}$ , if  $P_d$  of logic gate is dominant.

Thus the voltage lowering is effective to reduce  $P_d$  for low resolution ADC, However, it is still difficult to reduce  $P_d$  by reducing  $V_{DD}$  for high resolution ADC, even if SAR ADC architecture is used.

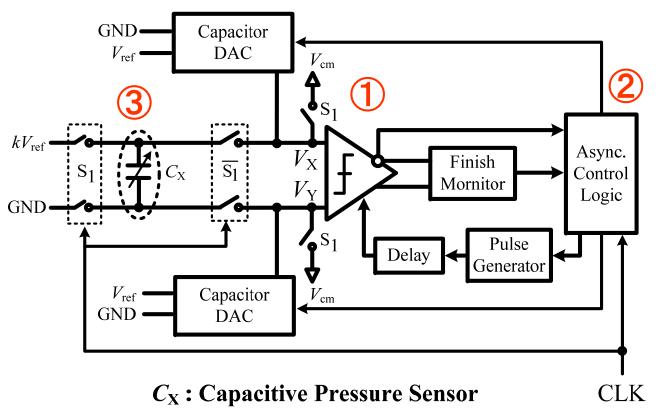

#### **Example: An ultra-low power CDC**

We have developed an ultra-low power Capacitance to Digital Converter.

- 1. 10b SAR like architecture

- 2. Self-clocking

- 3. Single to differential

#### 3nA @ 30 times/sec

Tuan Minh Vo, Yasuhide Kuramochi, Masaya Miyahara, Takashi Kurashina, and Akira Matsuzawa

"A 10-bit, 290 fJ/conv. Steps, 0.13mm22, Zero-Static Power, Self-Timed Capacitance to Digital Converter."

SSDM 2009, OC<sup>-</sup>

### Flash ADCs

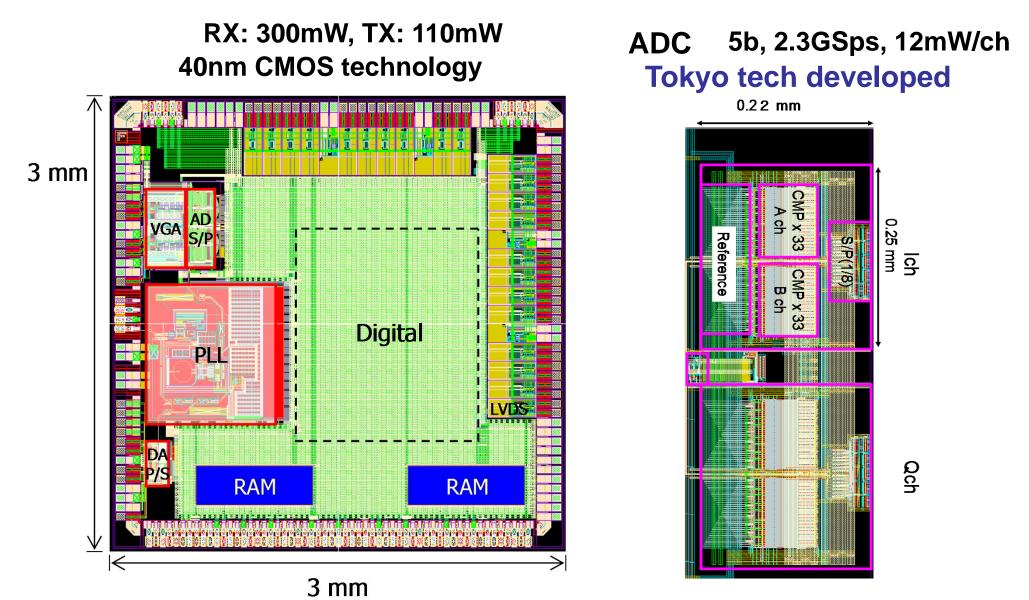

## **Developing baseband SoC**

# Developed chip for 60GHz transceiver integrating ADC, DAC, VGA, and PLL, using 40nm CMOS technology.

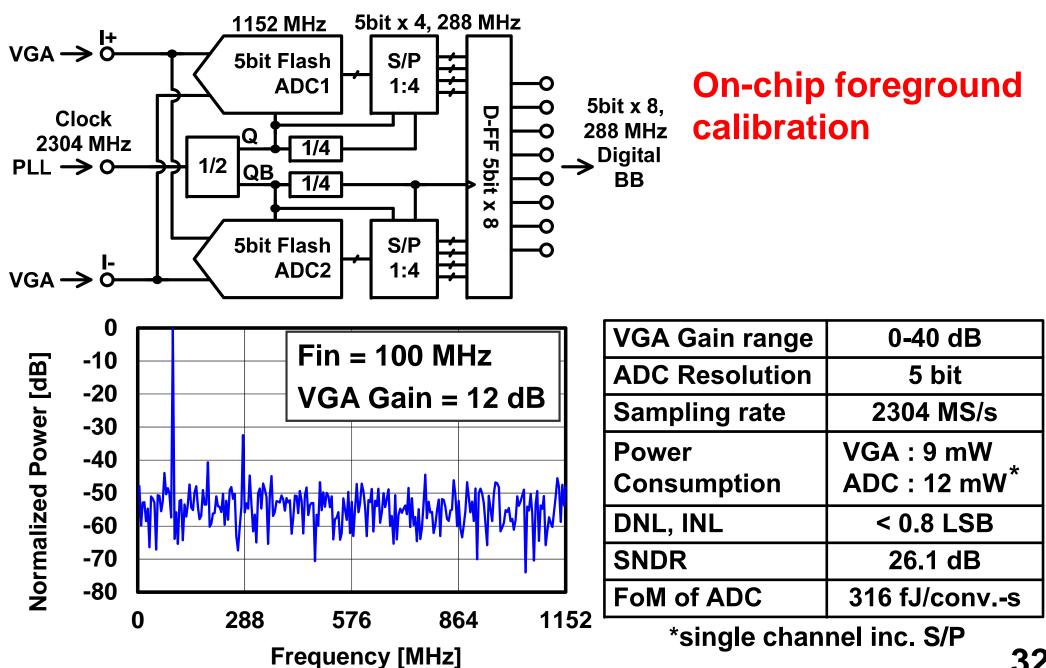

### **Analog Baseband : ADC**

# **ADC Comparison**

|              | Architecture         | Cal.     | fs<br>[GS/s] | SNDR<br>[dB] | Power<br>[mW] | FoM<br>[fJ/-c.s.] | Process<br>[nm] | Area<br>[mm <sup>2</sup> ] |

|--------------|----------------------|----------|--------------|--------------|---------------|-------------------|-----------------|----------------------------|

| [1]          | Flash                | -        | 3.5          | 31.2         | 98            | 946               | 90              | 0.149                      |

| [2]          | SAR                  | Internal | 2.5          | 34.0         | 50            | 489               | 45              | 1                          |

| [3]          | Folding              | Internal | 2.7          | 33.6         | 50            | 474               | 90              | 0.36                       |

| [4]          | Pipeline,<br>Folding | External | 2.2          | 31.1         | 2.6           | 40                | 40              | 0.03                       |

| [5]          | Flash                | Internal | 2.88         | 27.8         | 36            | 600               | 65              | 0.25                       |

| This<br>work | Flash                | Internal | 2.3          | 26.1         | 12            | 316               | 40              | 0.06                       |

[1] K. Deguchi, *et al.*, *VLSI Circuits* 2007 [2] E. Alpman, *et al.*, *ISSCC* 2009

[3] Y. Nakajima, *et al.*, *VLSI Circuits* 2007 [4] B. Verbruggen, *et al.*, *ISSCC* 2010

[5] T. Ito, *et al.*, *A-SSCC* 2010

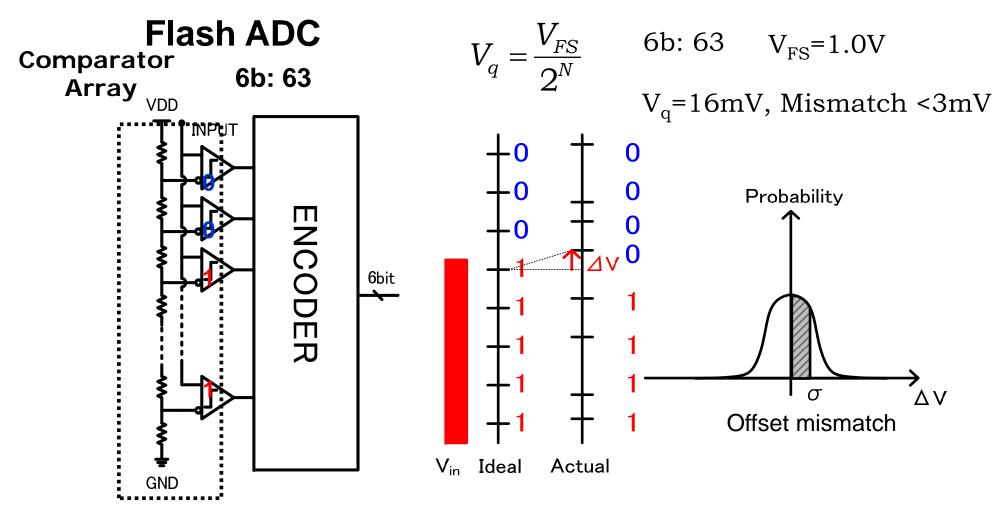

# Flash ADC

- Expecting highest speed

- Comparator determines the ADC performance

Offset mismatch mainly determines the effective resolution. Thermal noise can be neglected because of low resolution.

$N \leq 6$

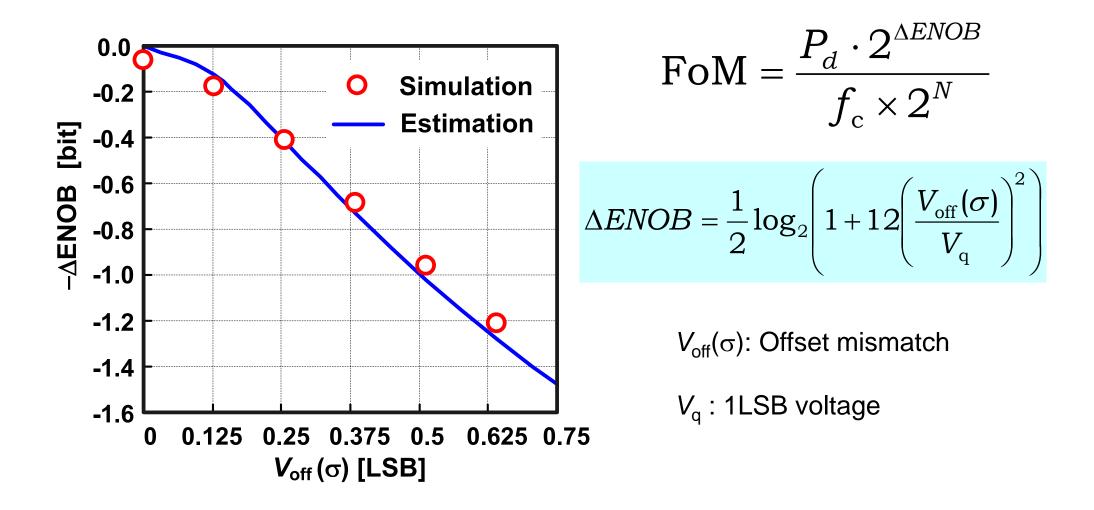

### **Performance of flash ADC**

FoM is degraded by the offset mismatch voltage of the comparator. Offset mismatch voltage should be reduced at low voltage operation.

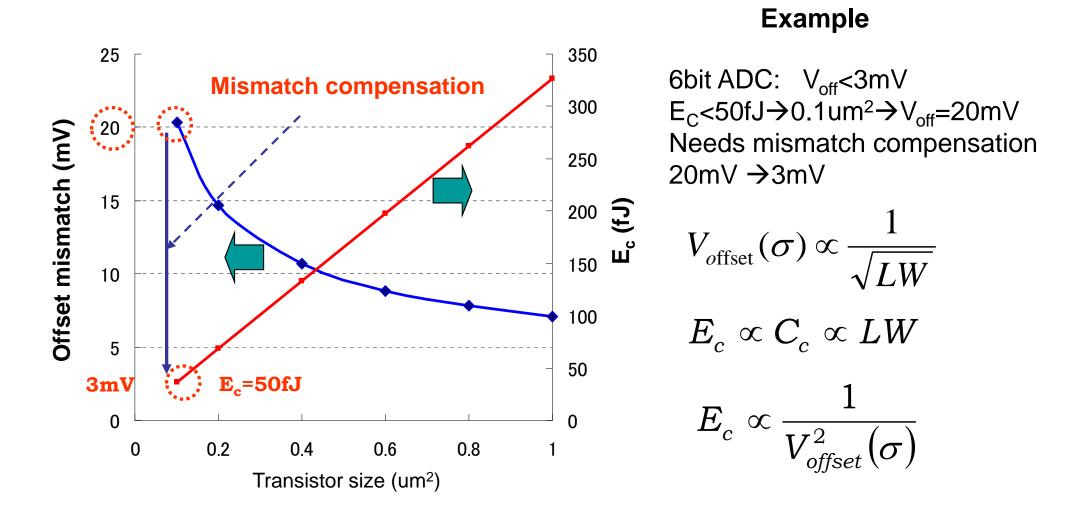

#### Tradeoff: mismatch and energy consumption 36

Serious tradeoff between mismatch of transistor and gate area.

Larger transistor is required to reduce mismatch voltage and results in increase of gate area and consumed energy.

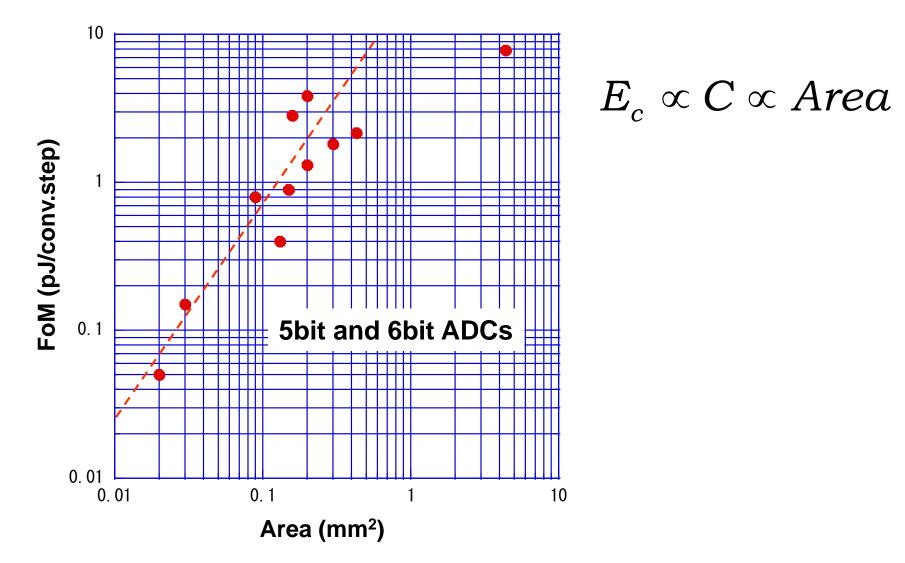

#### FoM vs. Area

Occupied area should be reduced to lower the FoM.

We must pay much attention to the occupied area.

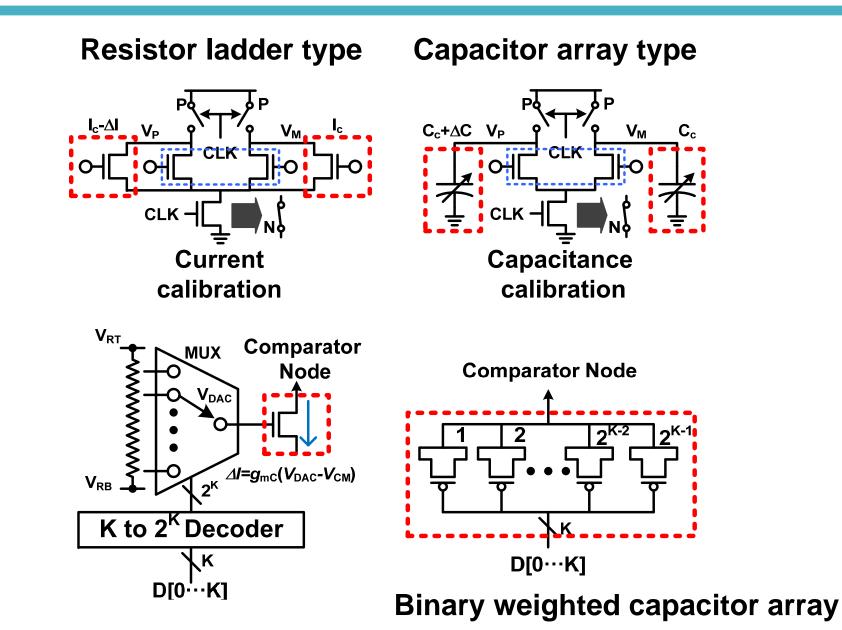

#### Mismatch compensation for the dynamic comparator

#### Digital calibration methods for mismatch 39

Y. Asada, K. Yoshihara,T. Urano, M. Miyahara and A. Matsuzawa,

"A 6bit, 7mW, 250fJ, 700MS/s Subranging ADC" A-SSCC, pp. 141-144, Nov. 2009.

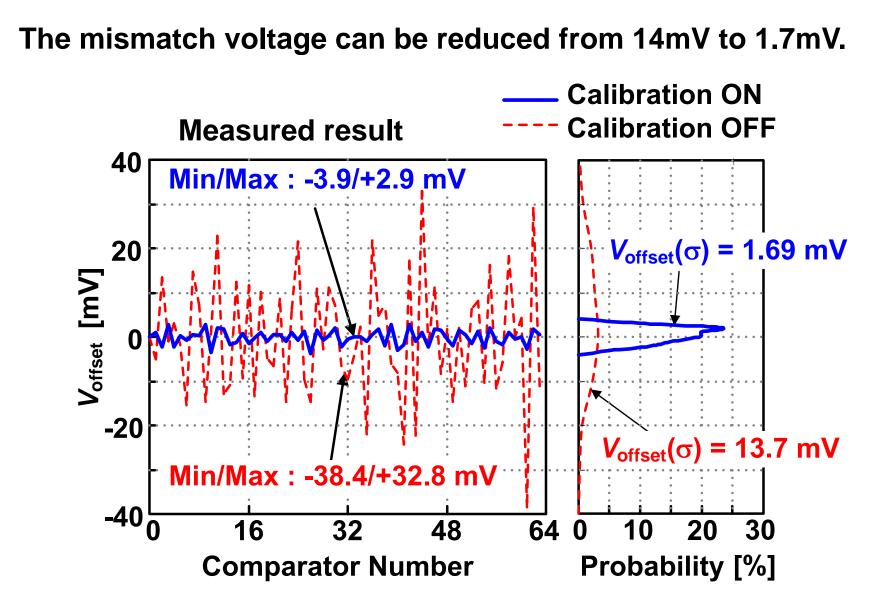

#### Effect of digital mismatch compensation 40

M. Miyahara, Y. Asada, D. Paik, and A. Matsuzawa, "A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs," A-SSCC, Nov. 2008.

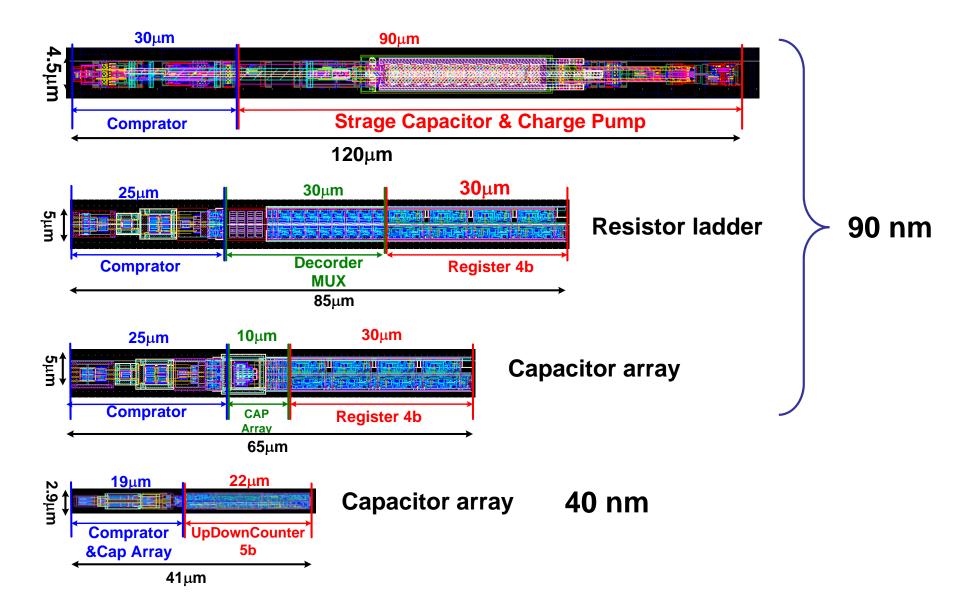

#### Area comparison

Penalty area for digital compensation will be reduced with technology scaling.

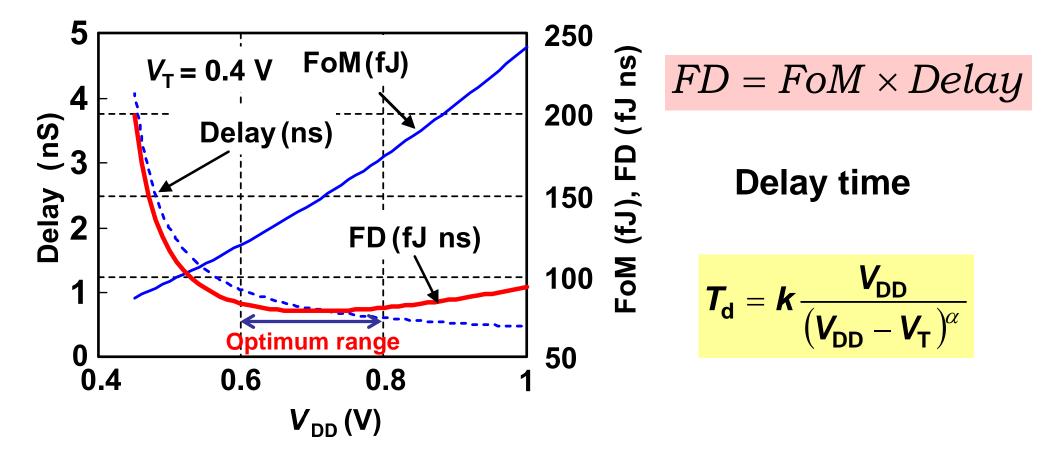

# FoM delay (FD) product

The FD product suggests the balance between the number of interleaving and decrease of energy consumption.

Delay is increased and the operating speed is lowered by reducing  $V_{\text{DD}}$

We should investigate the optimum  $V_{DD}$  by FD product.

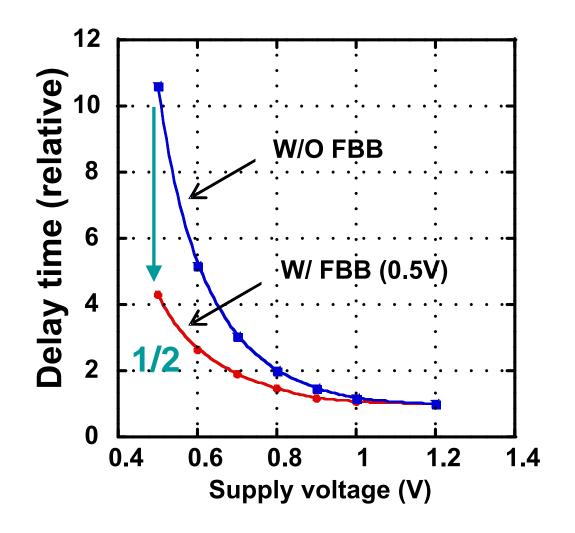

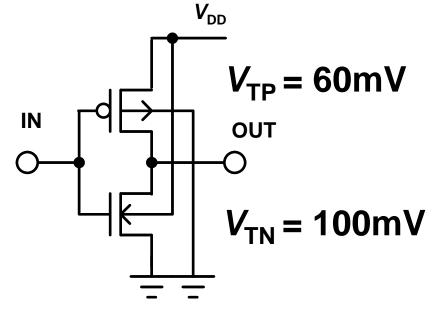

## Forward body biasing

Forward body biasing can decrease the delay time (1/2) and can be used easily at 0.5 V operation.

Increased leakage current in the proposed ADC is 0.32 mA by forward body biasing.

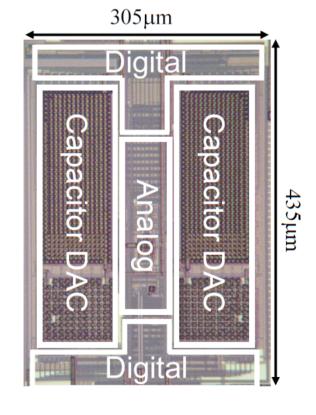

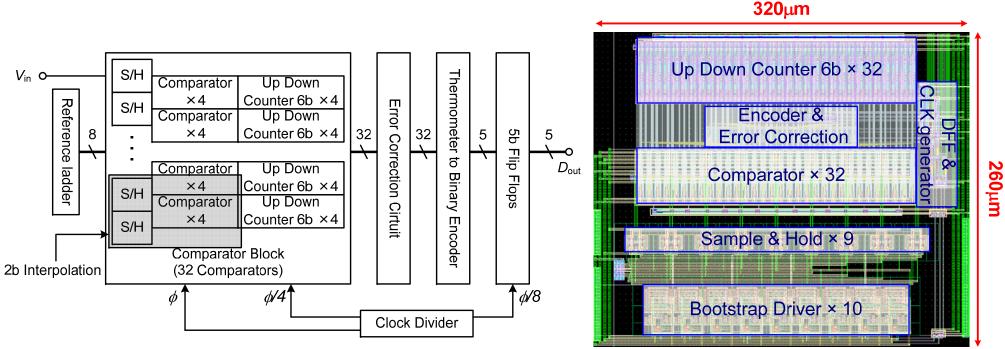

### **ADC Structure**

5bit 0.5V 600MSps Flash ADC is designed and fabricated in 90nm CMOS.

S/H circuits use gate boosted switches.

#### **Block diagram of ADC**

#### Chip microphotograph

M. Miyahara, J. Lin, K. Yoshihara, and A. Matsuzawa, "A 0.5 V, 1.2mW, 160fJ, 600 MS/s 5 bit Flash ADC" A-SSCC, pp. 177-180, Nov. 2010.

#### **Performance Summary**

#### A high speed and low FoM 0.5V flash ADC has been realized.

| Reference #                    | [7]  | [8]        | [9]   | [10]  | This work |

|--------------------------------|------|------------|-------|-------|-----------|

| Resolution (bit)               | 5    | 5          | 5     | 5     | 5         |

| fs (GS/s)                      | 0.5  | 1.75       | 1.75  | 0.06  | 0.6       |

| SNDR (dB)                      | 26   | 30         | 30    | 26    | 27        |

| Pd (mW)                        | 5.9  | 2.2        | 7.6   | 1.3   | 1.2       |

| Active area (mm <sup>2</sup> ) | 0.87 | 0.017      | 0.03  | -     | 0.083     |

| Vdd (V)                        | 1.2  | 1          | 1     | 0.6   | 0.5       |

| FoM(fJ)                        | 750  | 50         | 150   | 1060  | ,160      |

| CMOS Tech. (nm)                | 65   | 90         | 90    | 90    | / 90      |

| Architecture                   | SAR  | Fold+Flash | Flash | Flash | / Flash   |

[7] B. P. Ginsburg, J. Solid-State Circuits 2007.

[8] B. Verbruggen, ISSCC 2008.

[9] B. Verbruggen, VLSI Circuits 2008.

[10] J. E. Proesel, CICC 2008.

FoM<sub>Fmax</sub> = 160fJ @ 600MSps FoM<sub>Best</sub> = 110 fJ @ 360MSps

#### Summary of energy efficient ADC design 46

#### **Reducing static power**

Resistor DAC  $\rightarrow$  Capacitor DAC

**OpAmp based**  $\rightarrow$  **Comparator based**

**Reducing capacitance**

$\begin{array}{ll} E_d \approx CV_{DD}^2 & \text{ \# of CMP } \ \text{Flash} \rightarrow \text{SAR} \\ \\ \Delta V_T \propto \frac{1}{\sqrt{C_G}} & \text{TR size } & \text{Large TR} \rightarrow \text{Small TR with compensation} \\ \\ \overline{V_n} \propto \frac{1}{\sqrt{C}} & \text{Noise } & \text{Use complementally ckt.} \\ \\ \hline \text{Clock } & \text{Use self clocking} \end{array}$

#### **Reducing voltage**

Effective to digital gates and low resolution ADC

Use forward or adaptive body biasing