# A 0.5 V, 1.2 mW, 160 fJ, 600 MS/s 5 bit Flash ADC

James Lin, Kei Yoshihara, Masaya Miyahara, and Akira Matsuzawa

Matsuzawa and Okada Laboratory

Department of Physical Electronics, Tokyo Institute of Technology, Japan

## **5-bit Low-Voltage Flash ADC**

- **1.** An ultra-low power ADC is strongly required

- > Portable applications, ubiquitous wireless sensor systems, and green IT

- 2. A low-voltage operation is required for further technology scaling and low power operation

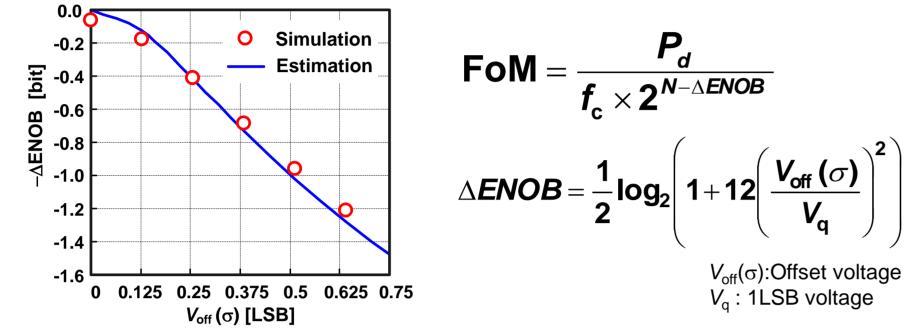

- **Fom of ADCs should be reduced like digital circuits** optimizing speed, resolution and power

- > Low-voltage calibration techniques are required

## **Low-Voltage Strategies**

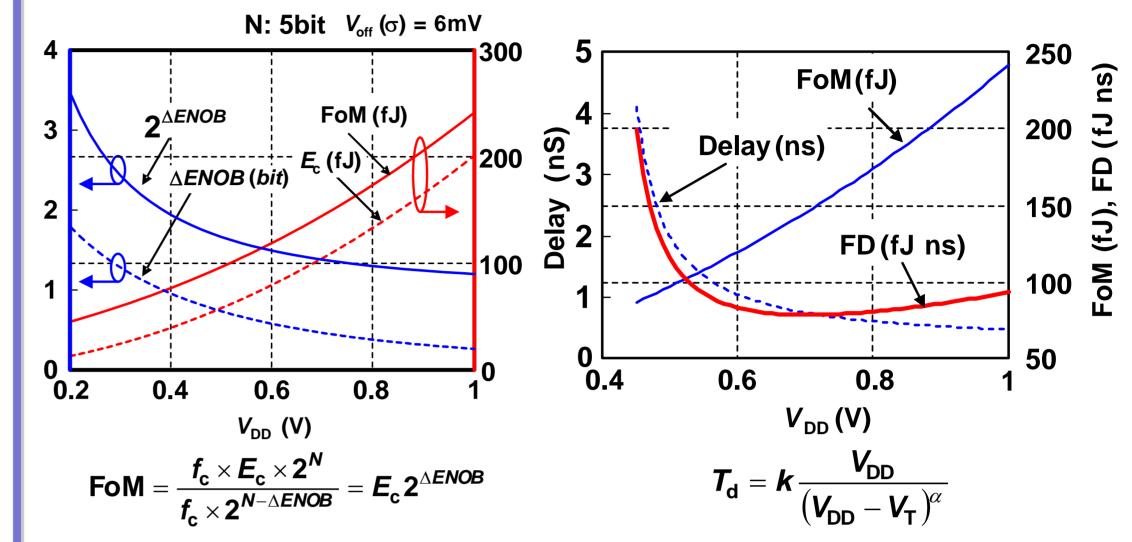

$\succ$  FoM can be significantly reduced with V<sub>DD</sub> lowering > The FoM-Delay (FD) product suggests the balance between the interleaving number and energy saving

Ec: Energy consumption for each comparator and followed logic circuits.

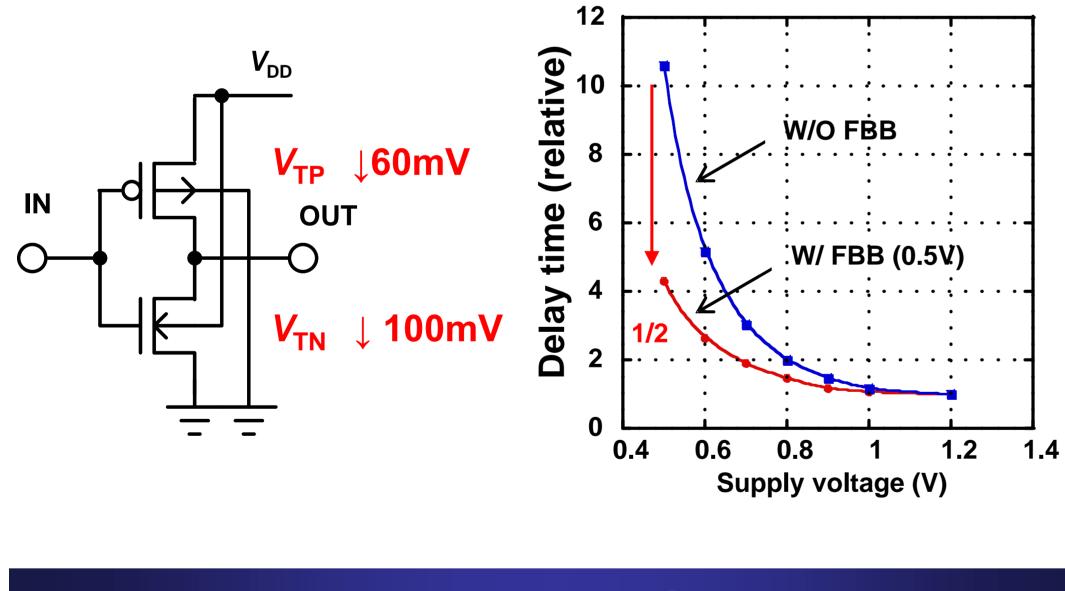

## Forward Body Biasing

#### > Advantages

- $\rightarrow$  Reduces the delay time to 1/2

- > Allows for 0.5 V operation by reducing V<sub>TP</sub> and V<sub>TN</sub> by 60 mV and 100 mV, respectively

### > Disadvantage

Leakage current in the proposed ADC is increased by 0.32 mA

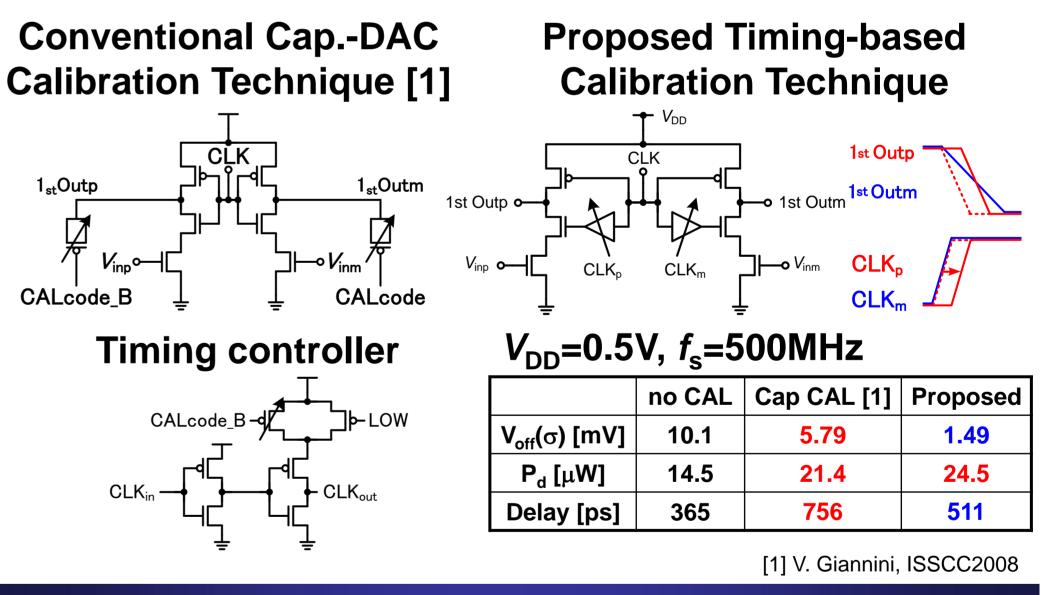

## **Timing-based Calibration**

- > Conventional capacitor DAC calibration [1] operating under low voltage

- > MOS varactor's sensitivity decreases

- > Delay time and power consumption increases

- Proposed timing-based calibration

- > Time is independent of supply voltage lowering > DNL/INL 2 LSB  $\rightarrow$  0.5 LSB

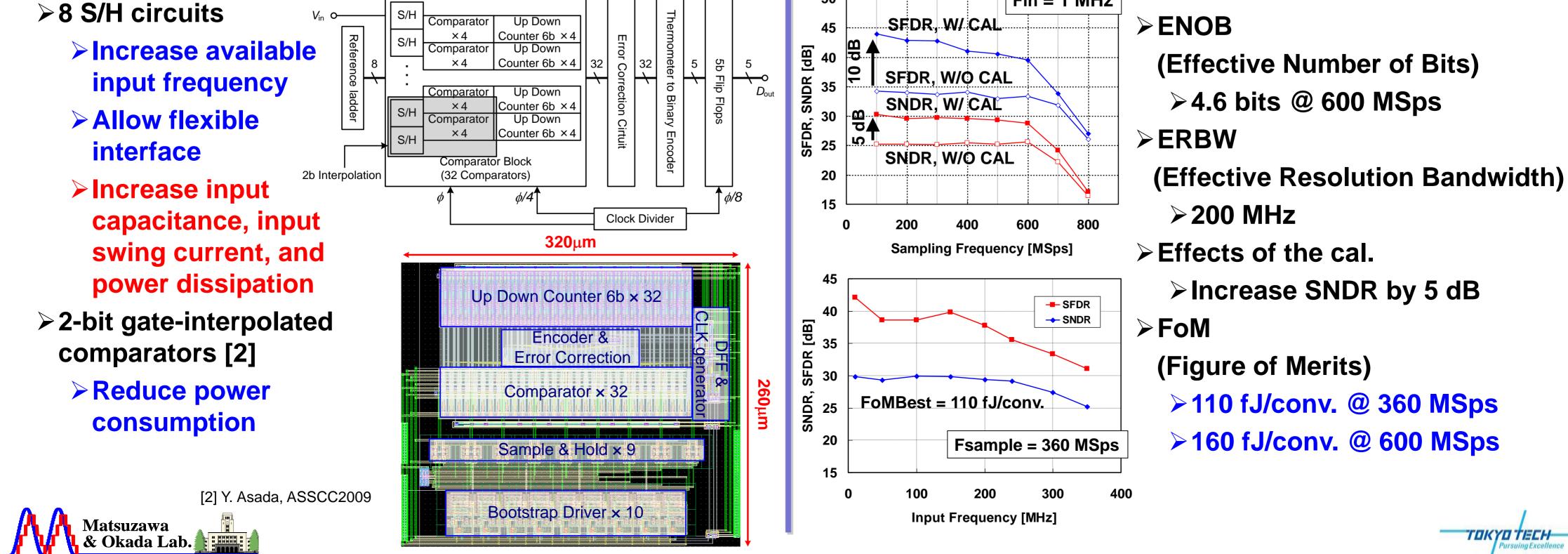

## **Overall Design**

## **Measurement Results of the 5-bit ADC**

Fin = 1 MHz

50