# A CMOS Direct Sampling Mixer Using Switched Capacitor Filter Technique for Software-Defined Radio

Hong Phuc Ninh, Takashi Moue, Takashi Kurashina, Kenichi Okada, and Akira Matsuzawa Department of Physical Electronics, Tokyo Institute of Technology 2-12-1-S3-27 Ookayama, Meguro-ku, Tokyo 152-8552 Japan. Tel/Fax: +81-3-5734-3764, E-mail: phuc@ssc.pe.titech.ac.jp

Abstract—This paper proposes a novel direct sampling mixer (DSM) using Switched Capacitor Filter (SCF) for multi-band receivers. The proposed DSM has a higher gain, more flexibility and lower flicker noise than that of conventional circuits. The mixer for Digital Terrestrial Television (ISDB-T) 1-segment was fabricated in a 0.18  $\mu$ m CMOS process, and measured results are presented for a sampling frequency of 800 MHz. The experimental results exhibit 430 kHz signal bandwith with 27.3 dB attenuation of adjacent interferer assuming at 3 MHz offset.

### I. Introduction

Nowadays, dozens of wireless communication standards, e.g. GSM, UMTS, WLAN, Bluetooth, GPS, DTV, and RFID, have been used in mobile terminals. Thus it indicates a need for a flexible mobile terminal that can support many wireless communication standards. However, the present multistandard terminal consists of several LNAs, VCOs, Mixers. As a result, it becomes more complicated and needs larger area and power comsumption. A multi-standard RF front-end implemented in a single chip is required for smaller size, lower power [1]. Software-defined radio (SDR) is focused to satisfy these requirements. The adoption of Muli-tap Direct Sampling Mixer (MTDSM), proposed recently by R.B. Staszewski, et al [2], is one of promising approaches for SDR. However, the conventional MTDSM consists of passive components, thus large gain loss and low order of the filter are unavoidable problems. Moreover, it is a little difficult to be applied to the wideband wireless applications, e.g. WLAN, UWB, etc, due to narrow pass-band characteristics of MTDSM. In addition the flicker noise is also a tough problem of the conventional MTDSM due to the passband characteristics. In this paper, we propose a MTDSM using Switched Capacitor Filter (SCF), which realizes more gain and flicker-noise supression. Moreover, SCF in the proposed MTDSM contributes to provide higher-order filtering, which can realize gain flatness over the in-band.

# II. PROPOSED DSM ARCHITECTURE

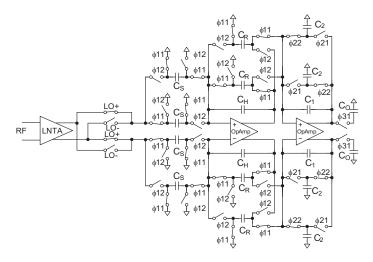

Fig. 1 shows the proposed sampling mixer architecture, where RF input signal is sampled, filtered and decimated. This mixer is based on current-mode direct sampling, thus a transconductance amplifier (TA) is used to convert the received

Fig. 1. The proposed direct sampling mixer.

RF voltage into current domain. The current gets sampled by the local oscillator and integrated into the sampling capacitor  $C_S$ . During the phase  $\phi 11$  (or  $\phi 12$ ), the sampled RF inputs are accumulated on one  $C_S$ , while the accumulated charge is read out to the next stage by another  $C_S$  in the same time. Thus, it performs a Moving-Average (MA) Filtering. Moreover, one capacitor  $C_R$  shares the charge with  $C_H$ , a "history" capacitor, and another  $C_R$  is read out. The total charge stored in  $C_H$  and  $C_R$  at phase  $\phi 11$  (or  $\phi 12$ ) is equal to the sum of the remaining charge in the "history" capacitor  $C_H$  in the previous one and the accumulated charge of the sampling capacitor. This operation introduces an IIR Filtering. The second MA Filtering and IIR Filtering is realized with the same method according to the opposite operating of phase  $\phi 21$  and phase  $\phi 22$  in the next stage.

In the conventional sampling mixer, DC and the harmonic frequency at multiple of local oscillator will also be aliased in with the sampled signal. Thus the DC component become large because of the affect of DC offset and 1/f noise. As shown in Fig. 1, RF input signal, RF+ and RF- are alternately input to the filter core in the SCF mixer. According to that, the frequency response of the proposed mixer is shifted by  $\pi$  and

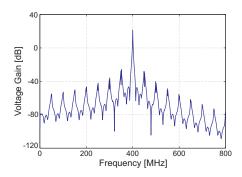

Fig. 2. Frequency response of SCF mixer.

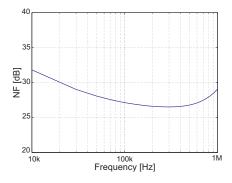

Fig. 3. The noise figure of SCF mixer.

Fig. 4. Chip micrograph of SCF mixer.

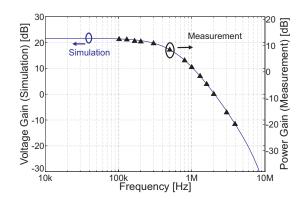

the aliased signal will not be aliased to the DC component, thus smaller DC component can be archieved. Fig. 2 and 3 show the frequency response and noise figure of the proposed mixer respectively, where the TA, OPAmps, switches and buffers were designed in MOS device but ideal digital clocking signals. The simulations were performed by using  $50\,\Omega$  input signal sources and  $50\,\Omega$  terminations. As shown in Fig. 2, the peak voltage gain is 21.6 dB, and in Fig. 3, NF is about 27 dB at 430 kHz.

# III. MEASUREMENT RESULT

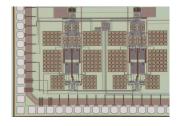

The proposed SCF direct sampling mixer has been designed for operation at 800 MHz sampling frequency and 430 kHz bandwith. A LNTA, where  $g_{\rm m}$  is 10 mS at sampling frequency, is also included. In addition, two LNTA+DSM for IQ mode are also developed. The mixers and LNTAs have been implemented in TSMC  $0.18\,\mu{\rm m}$  CMOS process. Fig. 4 shows a

Fig. 5. Down-converted frequency response of implemented SCF mixer.

TABLE I

DSM performance summary.

| Technology                     | TSMC $0.18\mu\mathrm{m}$ CMOS process       |

|--------------------------------|---------------------------------------------|

| Local Oscillator               | 800 MHz                                     |

| Bandwith                       | 430 kHz                                     |

| Power Gain@400.1 MHz input     | 12.4 dB                                     |

| Attenuation@3 MHz offset       | 27.3 dB                                     |

| Supply voltage V <sub>DD</sub> | 1.8 V                                       |

| LNTA+DSM core current          | 18∼ 20 mA                                   |

| Power consumption              | 32.4∼ 36 mW                                 |

| Chip area                      | $1150\mu\mathrm{m} \times 750\mu\mathrm{m}$ |

chip micrograph of the implemented circuit. The core size is  $1150 \, \mu \text{m} \times 750 \, \mu \text{m}$ .

Two Signal Source Analyzers (Rohde & Schwarz SML02) and Spectrum Analyzer (Advantest R3267) were used for measurement. Fig. 5 shows down-converted frequency response of the mixer. Because of the matching problem of the TA and the output buffer, the conversion gain (power gain) of the implemented SCF mixer is small, about 12.4 dB at 400.1 MHz input. However, the measured results have the same tendency with the simulation, as shown in Fig. 5. Table I summarizes the measured results.

# IV. Conclusion

This paper has proposed a novel direct sampling mixer using SCF with 1/f noise suppression for software-defined radio. The proposed DSM is implemented in  $0.18\,\mu\mathrm{m}$  CMOS process. Measurement results show that the circuit works correctly and the experimental results exhibit  $430\,\mathrm{kHz}$  signal bandwith with  $27.3\,\mathrm{dB}$  attenuation of adjacent interferer assuming at  $3\,\mathrm{MHz}$  offset.

# ACKNOWLEDGMENT

This work is supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design Systems, Inc.

# REFERENCES

- H. Eul, "ICs for mobile multimedia communications," Proc. of IEEE International Solid-State Circuits Conf., Feb. 2006, pp. 31–35.

- [2] R. B. Staszewski, et al., "All-Digital TX Frequency Synthesizer and Discrete-Ti me Receiver for Bluetooth Radio in 130-nm CMOS," *IEEE Journal of Solid-State Circuits*, Vol. 39, No. 12, pp. 2278-2291, Dec. 2004.