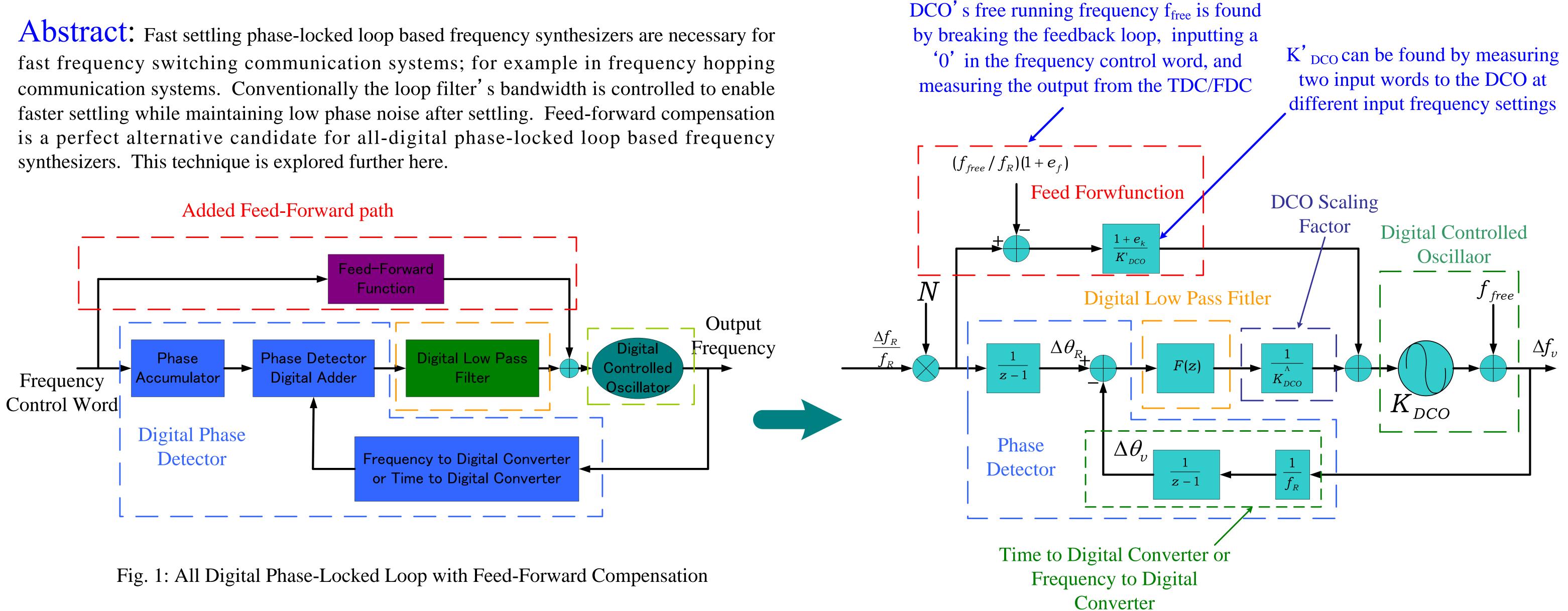

## **Feed-Forward Compensation for All Digital Phase-Locked** Loop based Synthesizers

Win Chaivipas, Akira Matsuzawa, and Philipus Chandra Oh

Dept. of Physical Electronics Tokyo Institute of Technology, Tokyo Japan

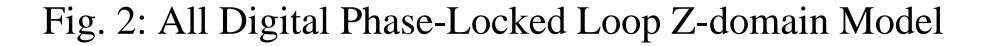

The output of the ADPLL without the feed-forward path can be shown to be related to the input by the following equation

$$\Delta f_{v} = \frac{\left(N \cdot F(z) \cdot K'_{DCO}\right)}{f_{R} \cdot (z-1) + F(z) \cdot K'_{DCO}} \cdot \frac{\Delta f_{R}}{f_{R}} + \frac{f_{free} \cdot (z-1) \cdot f_{R}}{f_{R} \cdot (z-1) + F(z) \cdot K'_{DCO}}$$

With the Feed-Forward Path and setting the DCO scaling factor to the reference frequency f<sub>R</sub> and complete compensation by exact prediction of DCO gain and offset

$$\Delta f_{v} = N \cdot f_{R} \cdot \frac{\Delta f_{R}}{f_{R}}$$

In reality however, this is not possible due to the finite precision of the digital circuitry, and error in gain prediction. With prediction and precision error, the system's response then becomes

$$\Delta f_{v} = \frac{\Delta f_{R}}{f_{R}} \cdot N \cdot f_{R} + \frac{\Delta f_{R}}{f_{R}} \cdot N \cdot f_{R} \frac{e_{k} \cdot (z-1) \cdot f_{R}}{(z-1) \cdot f_{R} + F(z) \cdot K'_{DCO}}$$

$$- \frac{(e_{k} + e_{f} + e_{f} \cdot e_{k}) \cdot (z-1) \cdot f_{R}}{(z-1) \cdot f_{R} + F(z) \cdot K'_{DCO}} f_{free}$$

$\Delta f_{i}$ **Output Expected Frequency**

Frequency Multiplication NFactor  $\Delta f_R$ Input Frequency time step  $f_{\scriptscriptstyle R}$ F(z)Low-Pass Filter Transfer Function **DCO Free Running Frequency**

- DCO gain prediction error  $e_{\scriptscriptstyle K}$

- $K'_{DCO} = \frac{K_{DCO}}{\Lambda}$ Normalized DCO gain  $K_{DCO}$ DCO Gain  $K_{DCO}$ **DCO Scaling Factor**

- **Reference Frequency**

$f_R$

$e_{f}$

**DCO Offset frequency** prediction error

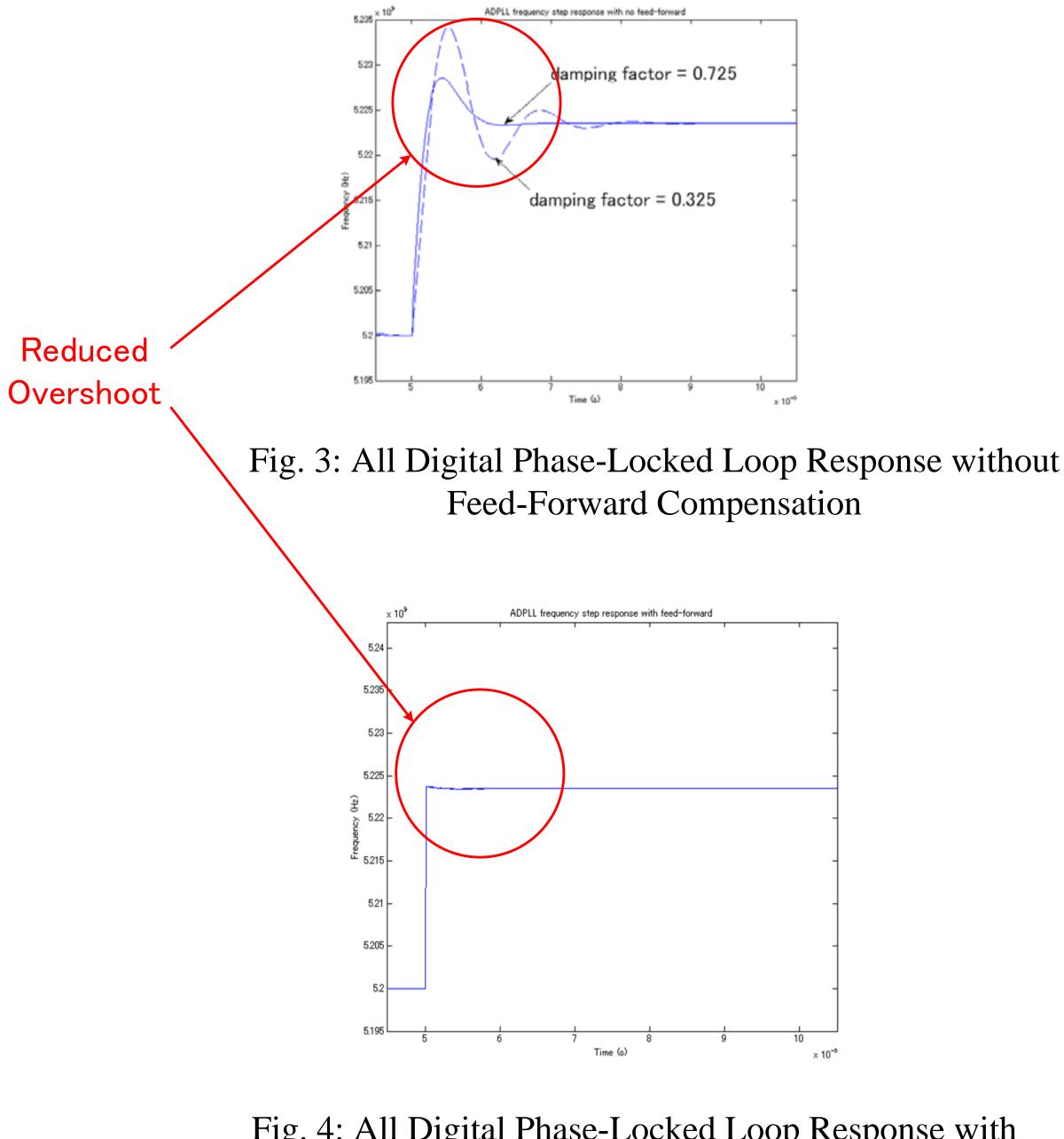

Fig. 4: All Digital Phase-Locked Loop Response with Feed-Forward Compensation

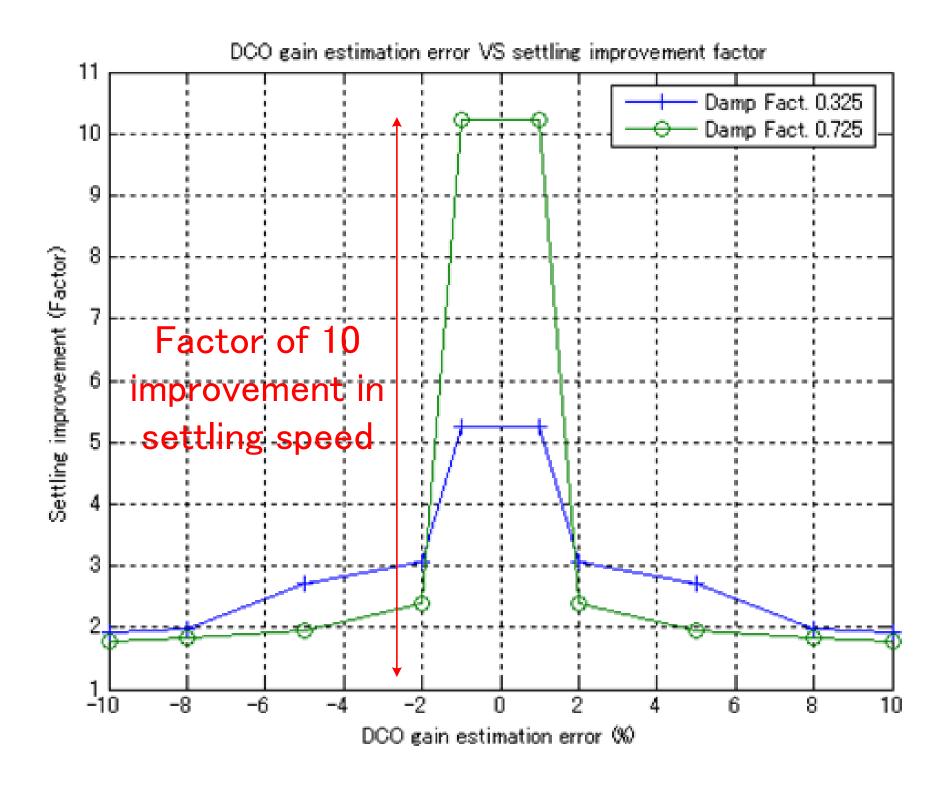

Fig. 5: All Digital Phase-Locked Loop Settling time improvement VS DCO gain estimation error

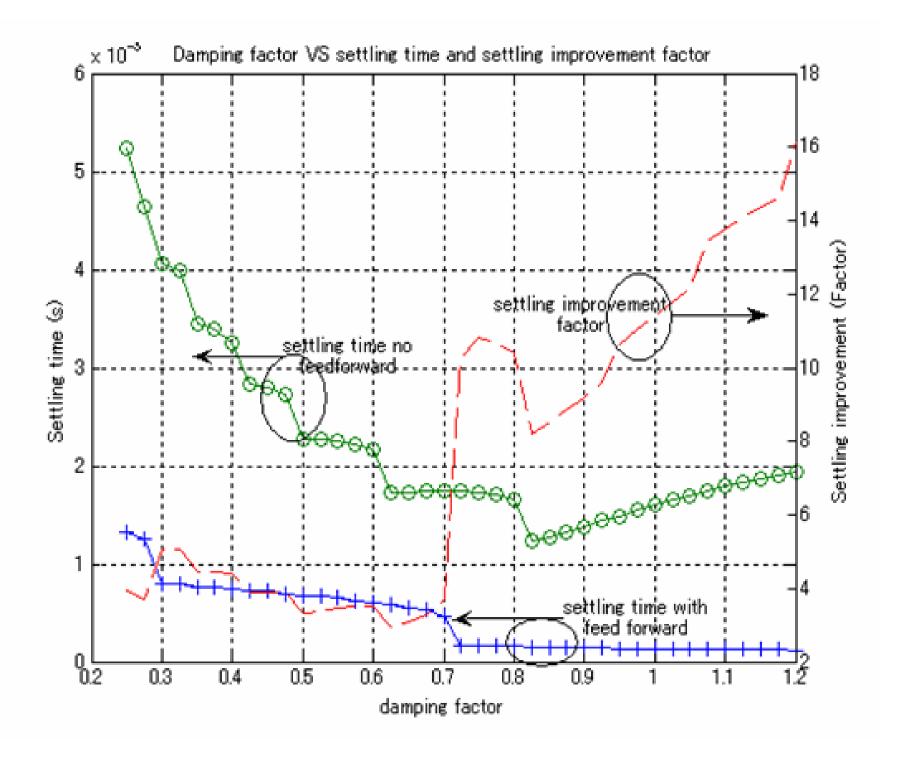

Fig. 6: All Digital Phase-Locked Loop Settling time and improvement factor VS damping factor at 1% DCO gain prediction error