# Lessons and Challenges for Future Mixed-Signal, RF, and Memory Circuits

#### Akira Matsuzawa

### **Tokyo Institute of Technology**

VLSI panel, A. Matsuzawa

# Can we verify the analog circuits perfectly by circuit simulator?

# Pitfalls of Analog IC Design

2

- Bugs of system level design

- Lack of well device models

- Wrong circuit simulation

- Effects of parasitic components

Not only in IC but also external components (package, PCB, etc.)

- Influences of EM fields

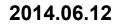

## Ex.1 Hung-up: wrong system level design 3

# 50MS/s SAR ADC suddenly stopped after 1 hour from power-on . Error rate: $10^{-11} \leftarrow$ Can we simulate?

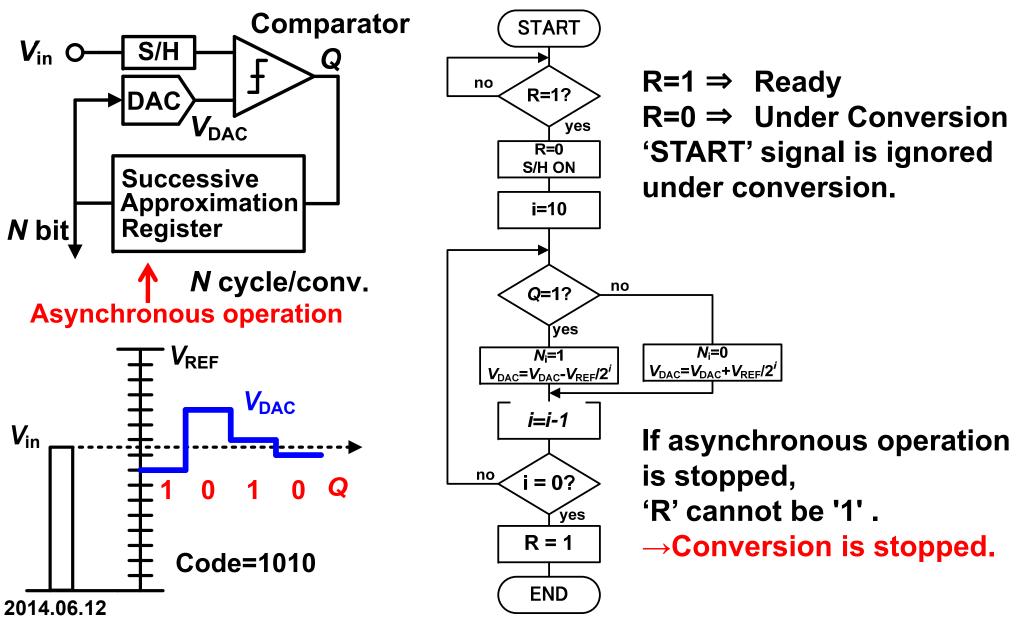

## **Ex.2 Wrong circuit simulation**

2014.06.12

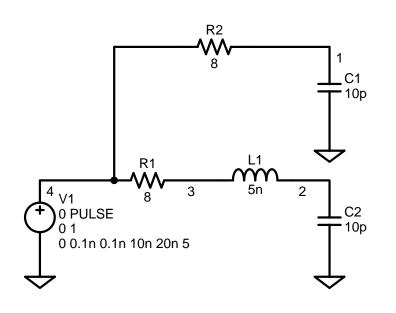

# **Ex.3 Different result: Effect of inductance** 5

If inductance is neglected, The smaller resistance is the better for fast settling. However, actual circuit contains Inductive component; wires. If it is considered, Smaller resistance makes large Ringing. The optimum resistance exists.

VLSI panel, A. Matsuzawa

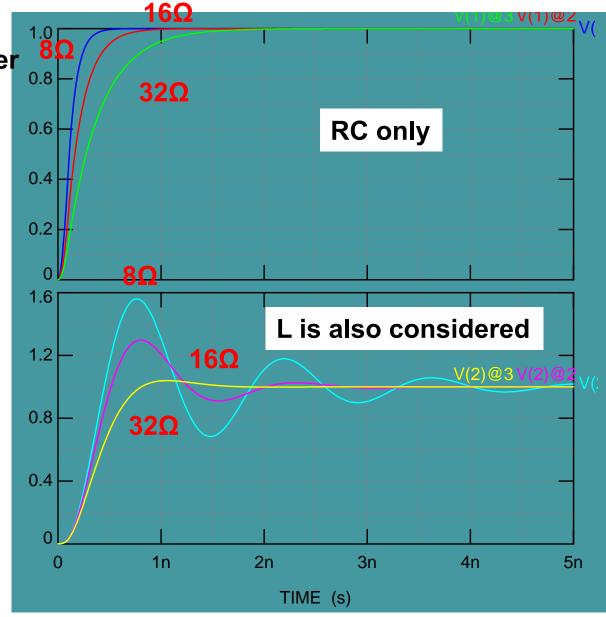

#### **Ex.4** Parasitic components

2014.06.12

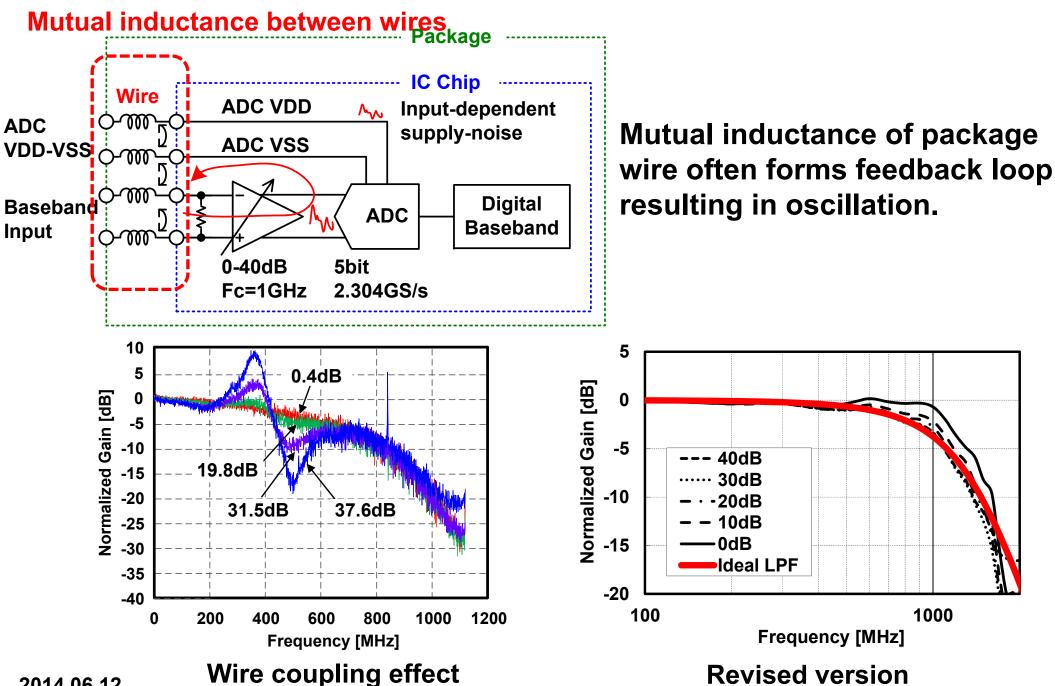

# Small design margin: VT of transistor 7

VT of 40nm CMOS transistor is quite high of 0.6V. ( $V_{GS}$ =0.8V) PVT variation is 220-240mW.

Therefore it is quite difficult to realize 1V operation with 40nm CMOS.

VLSI panel, A. Matsuzawa

# Reality of analog& mixed signal LSI

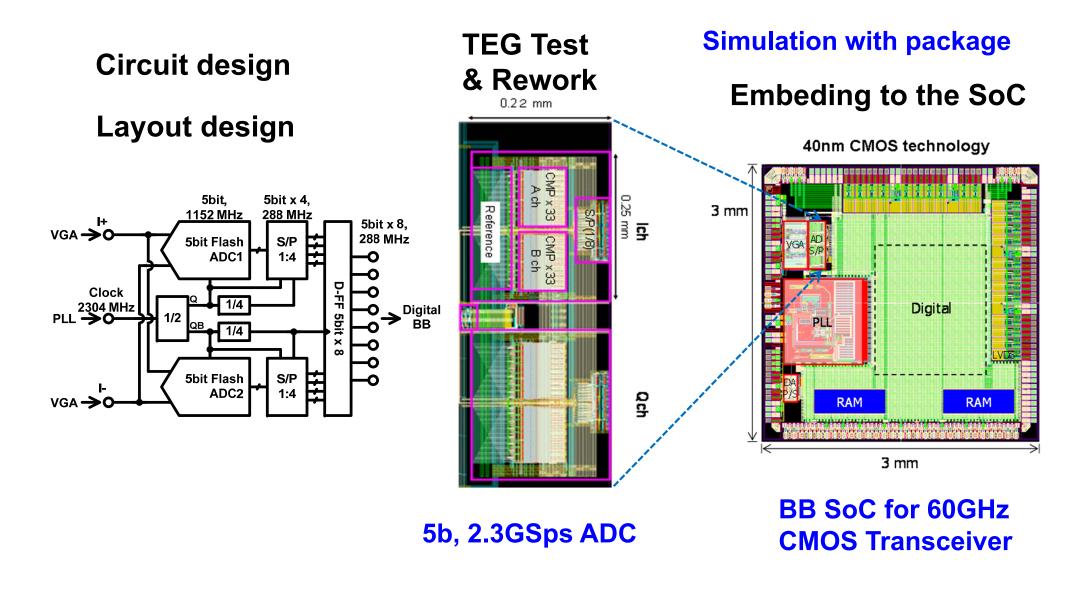

#### Circuit design

- Almost no margin for low voltage design.

- Can't simulate every performance with every condition.

- Calibration technique is needed, however it can't guarantee the optimum performance.

#### Layout design

- Analog performance is strongly affected by layout design.

- Package and board design affects the performance.

- Not acceptable time for LPE simulation.

- Testing and embedding

- No testing method for perfect verification.

- Strongly affected by package or probe.

- Affected by embedding to Mixed signal LSI.

### **Development procedure of M/S SoC**

TEG test and rework are necessary before embedding to the M/S SoC.