# SoC and SiP technology for digital consumer electronic systems

Akira Matsuzawa

**Tokyo Institute of Technology**

#### **Contents**

- Digital consumer electronic systems and SoC

- SoC technology for the future digital consumer electronic systems

- Module and SiP technology for the future digital consumer electronic systems

- Development management

# Digital consumer electronic systems and SoC

# Digital consumer era

The digital consumer era has emerged.

#### **Contribution of SoC**

SoC has contributed to the commercialization of the digital consumer technology. The performance has increased and the cost has decreased, drastically.

Model; Year of 2000

Model; Year of 2003

#### Position of SoC in CE electronics

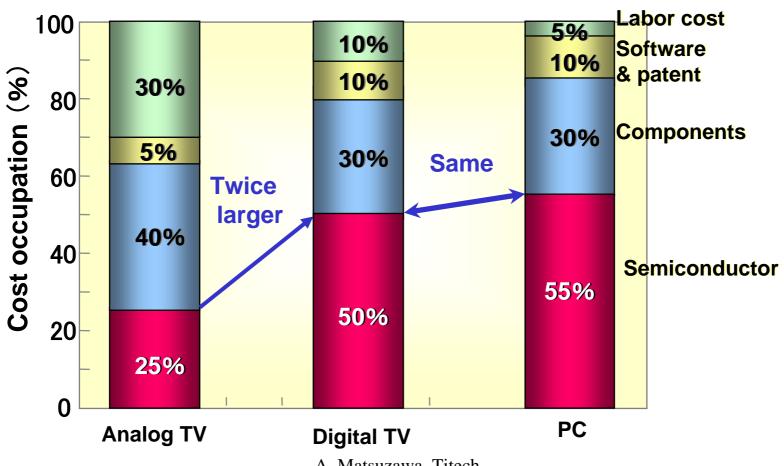

The digitalization of the CE systems have raised the position of the semiconductor and SoC. About 50% of total cost is due to semiconductors.

2005 06 20 A. Matsuzawa, Titech

6

# SoC technologies for digital CE

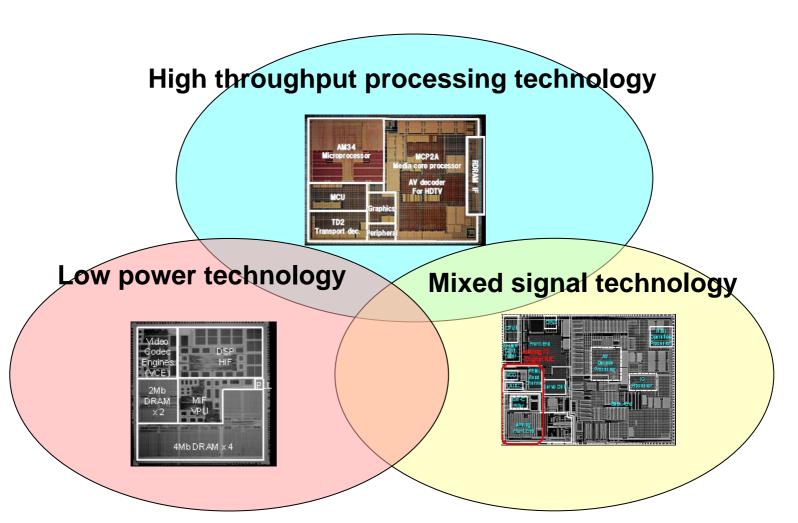

Digital CE systems need these basic SoC technologies.

#### Needed performance for digital video

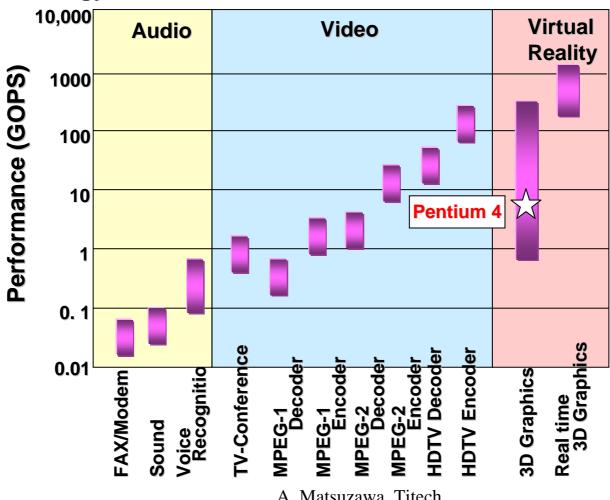

Necessary performance for the digital video system is one or two order higher than that of PC. Digital CE systems have needed for the progress of the LSI technology.

8

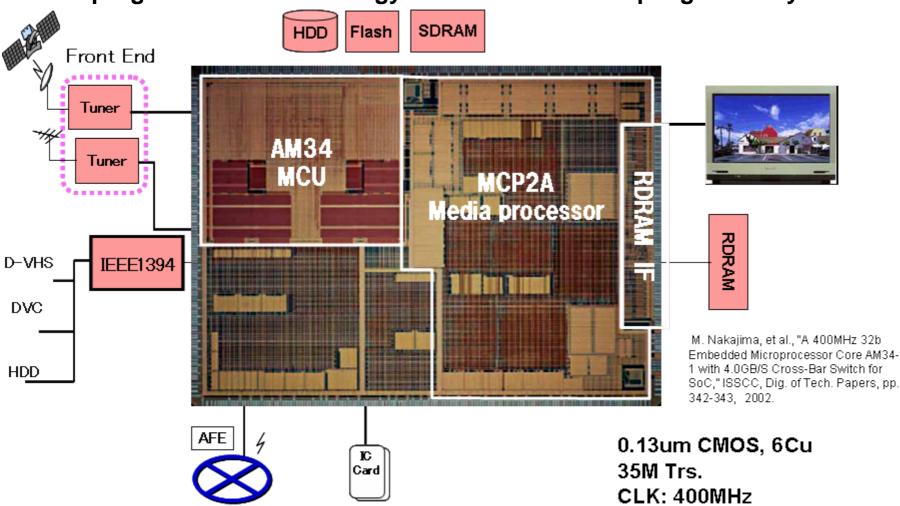

# **SoC for Digital TV systems**

The progress of LSI technology has realized one chip digital TV systems.

#### Low power SoC

#### Low power, yet high performance SoCs are required for the CE systems.

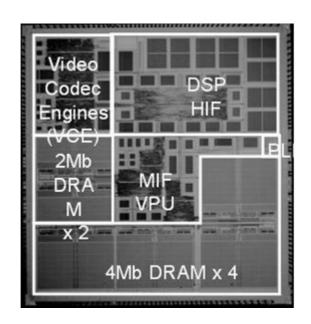

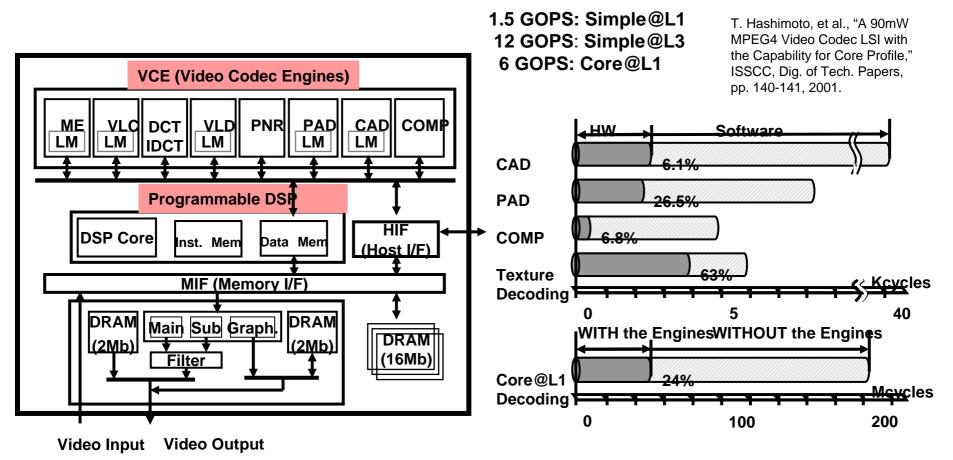

#### MPEG4 Codec

0.18um e-DRAM 31M Tr **90 mW@54MH**z

1.5 GOPS: Simple@L1 12 GOPS: Simple@L3 6 GOPS: Core@L1 T. Hashimoto, et al., "A 90mW MPEG4 Video Codec LSI with the Capability for Core Profile," ISSCC, Dig. of Tech. Papers, pp. 140-141, 2001.

#### MPEG4 Decoder

0.18um CMOS 11M Tr **11 mW@27/54MH**z M. Ohashi, et al., "A 27MHz 11.1 mW MPEG4 Video Decoder LSI for Mobile Application," ISSCC, Dig. of Tech. Papers, pp. 366-367, 2002.

15fps (Core@L1 decode)

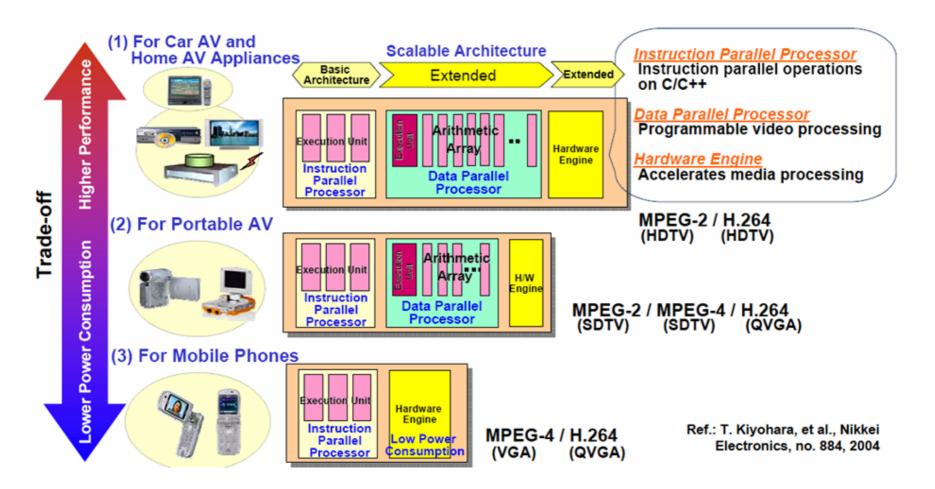

# Low power technology

Low power and high performance architecture dedicated for the application has been developed.

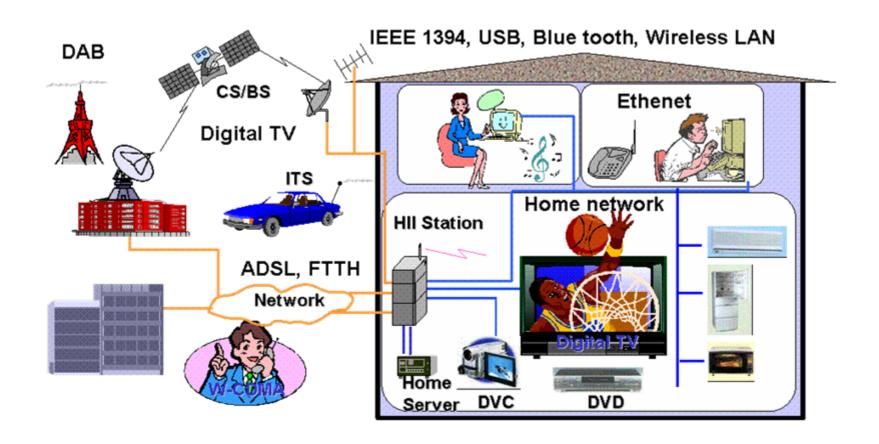

# Digital network society

The digital network era has emerged. All digital consumer systems will connect each other through the networks.

The mixed signal (RF) technology plays an important role.

# Mixed signal technology

Current electric systems need the mixed signal technology. SoC needs analog circuits.

- Digital networks, communication, broad casting (DTV, ADSL, Ethernet, USB)

- Digital recording (HDD, DVD, DVC)

- Digital camera and display

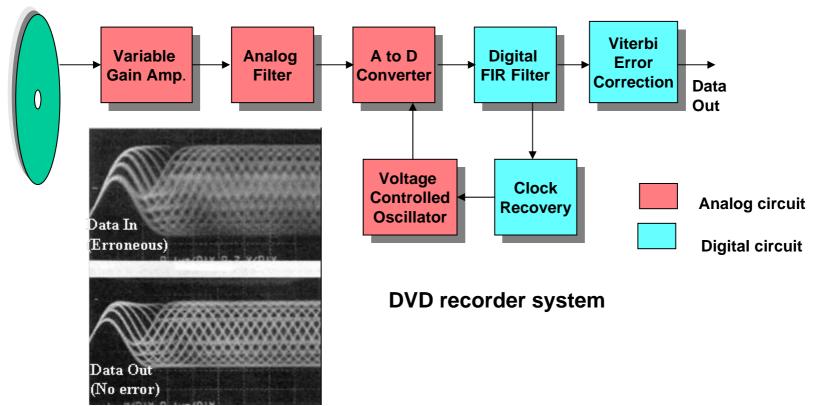

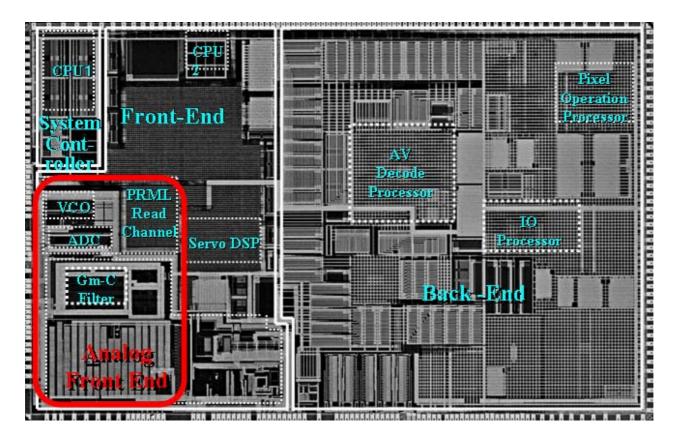

#### Mixed signal SoC

The mixed signal SoC technology has realized one chip DVD system.

0.13um, Cu 6Layer, 24MTr

Okamoto, et al., ISSCC 2003

# SoC technologies for digital CE

Digital CE systems have been realized by the progress of SoC technology.

**System requirements**

**SoC technologies**

High throughput processing

10-100 GOPS

Low power

2-3 W for conventional 100mW for portable

Total system on a chip

Analog and interface

**Technology scaling**

Moor's law

Dedicated architecture for the application

Massive parallel

Media processor

Dedicated processor engine

Mixed signal technology

On-chip analog RF-CMOS

SoC

for Digital CE

#### **Function of Consumer Electronics**

Audio recording and playback

Video recording and playback

Putting broadcasting programs on Radio or TV

**Personal communication**

Personal amusement

#### **Essential trends of consumer electronics**

Lighter, Smaller, Cheaper

Military → Industrial → Home →Personal →Portable

Vacuum tube →Transistor →IC →LSI →SoC

→ Solid state

( CRT → LCD, EL)(Tape → MD → HDD → Semiconductor memory)

17

Single function → Multi functions (Cellular phone)

**Analog** → **Digital** → **Network**

#### **Digitalization**

#### Free from the materials

Analog depends on the materials, however digital is free from the materials.

- Multiple use without degradation → Copy issues

- The fabrication technology doesn't affect the quality so much

- → Easy to make → Rapid cost decrease

#### Unification

Once digitized, data looses its native properties.

- Loosing individuality and going unification

- Move to the software oriented technology

- Networking and broadcasting

# SoC technology for the future digital consumer electronic systems

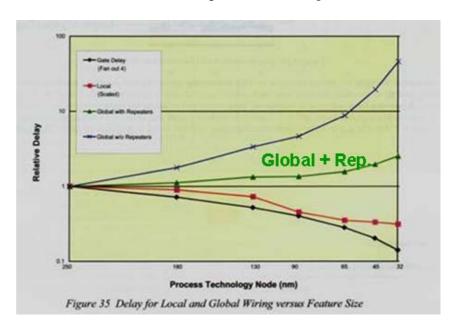

# **Biggest Crisis of LSI technology**

Power consumption has already reached the limitation.

The wire delay can't be reduced any more.

These will change the SoC architecture.

#### **Power consumption of MPU**

####

#### Wire delay roadmap

Gordon E. Moore, ISSCC 2003.

**ITRS 2001 Edition, pp. 261.**

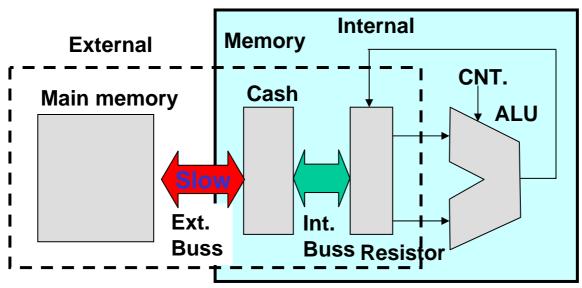

#### Processor system structure

Issue: 2 or 3 operations / clock (Very slow)

High throughput  $\rightarrow$  High freq.  $\rightarrow$  High power consumption.

Solution: Parallel processing units, multi-core, PE engine.

Issue: Memory access time takes 3x longer time than execution time.

Solution: CoC technology, instead of conventional ext. buss.

#### Micro processor system

#### Architecture and power consumption

The power crisis is not only due to the device technology but also due to the SoC architecture.

Software oriented Hardware oriented SoC for CE MPU for PC **DSP Parallelism** 16 96 0.9 8.0 2.4 **GOPS** Pd (mW) 110 12 7000 138 7800 Pd (mW)/GOPS 3 order's magnitude of difference

Courtesy, Prof. Brodersen, UCB

22

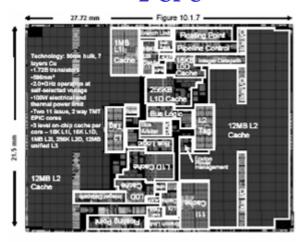

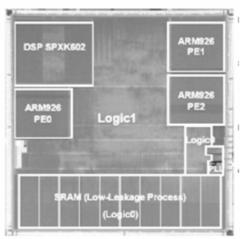

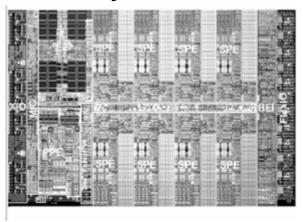

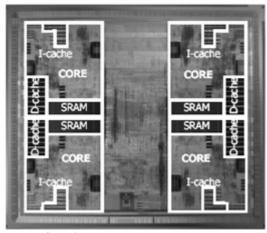

# **Multi-core processor**

Several multi-core processors were announced on ISSCC 2005.

Intel 2 CPU

NEC 3 CPU

IBM, Sony, Toshiba (1+8) CPU

Fujitsu 8W VLIW

2005 06 20 A. Matsuzawa, Titech

23

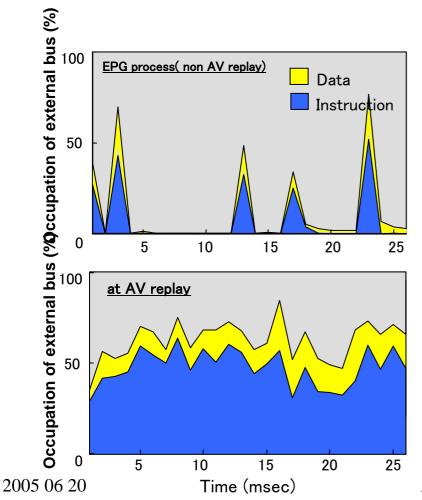

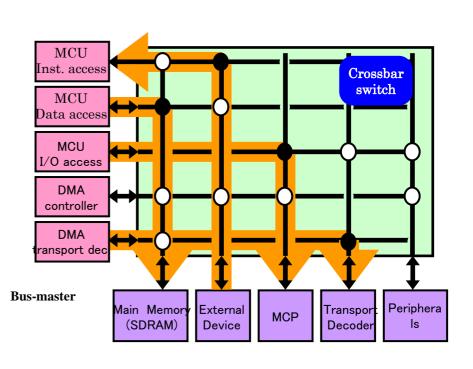

#### **Dedicated buss structure**

The occupation of an external buss at the AV processing is unacceptably high compared with that at the conventional PC processing.

Dedicated crossbar switch can increase processing throughput by a factor of 2.

A. Matsuzawa, Titech

#### Convergence to cellular phone

Cellular phones will integrate almost all digital consumer functions.

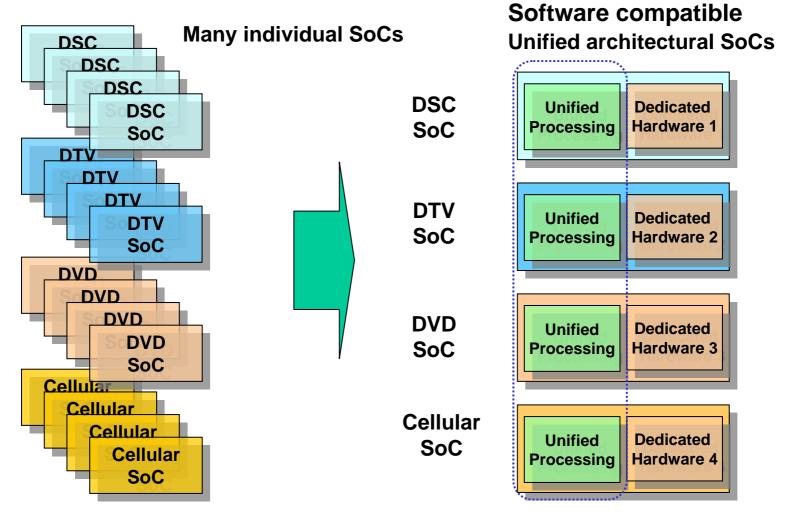

# Direction of SoC for digital CE

Future SoC will use unified processor and dedicated circuits for several applications to increase the software development efficiency.

# Unified architecture for digital CE

#### An unified and a scalable architecture is the direction.

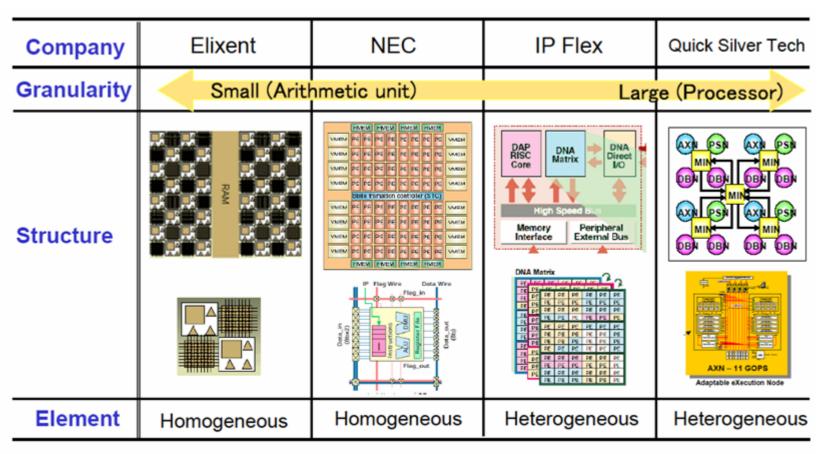

# Reconfigurable logic

#### Reconfigurable logics will be embedded onto SoC,

Ref.: Website of each company, see the last page.

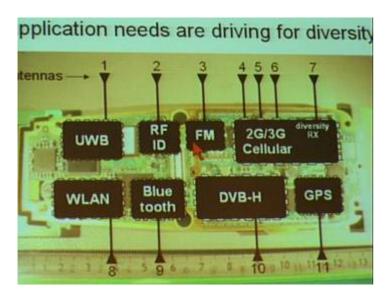

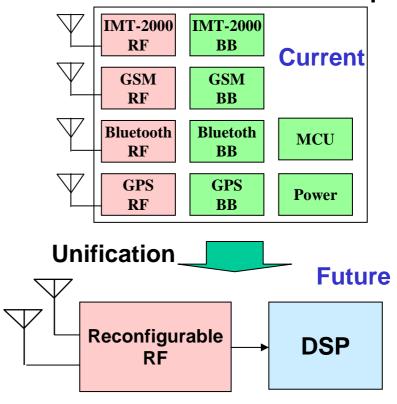

#### Wireless communication

Cellular phones must need many wireless standards in the future.

RF circuits and DSP should be unified.

Re-configurability and Programmability are keys.

# Future cellular phone needs 11 wireless standard!!

Yrjo Neuvo, ISSCC 2004, pp.32

#### Multi-standards and multi chips

**Unified wireless system**

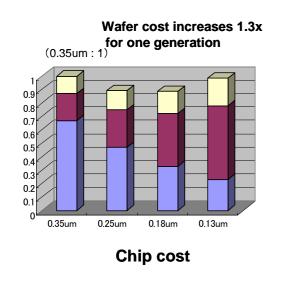

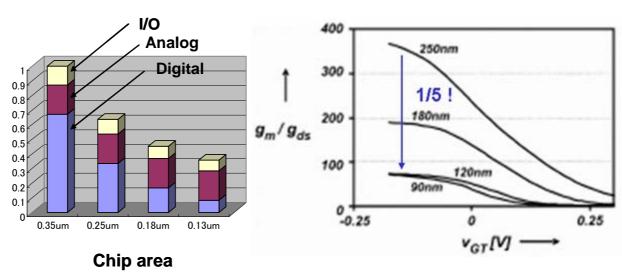

#### Issues of mixed signal technology

Mixed signal technology will continue to be needed to realize the interface, communications, and the network. However many issues will be faced.

- 1) Cost increase due to the difficulty of area reduction

- 2) Low voltage operation (<1.2V)

- 3) Low dynamic range

- 4) Low voltage gain

#### Voltage gain

30

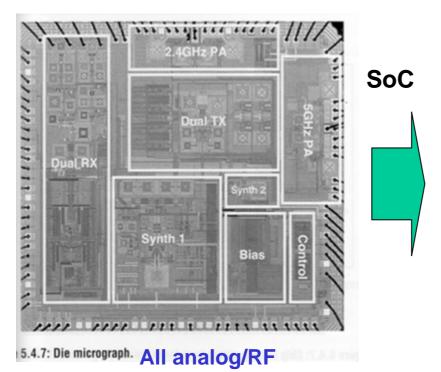

#### Recent RF CMOS LSI

Mixed signal SoC has emerged for wireless communication systems. Small analog/RF circuits is a key.

Wireless LAN, 802.11 a/b/g 0.25um, 2.5V, 23mm<sup>2</sup>, 5GHz

M. Zargari (Atheros), et al., ISSCC 2004, pp.96

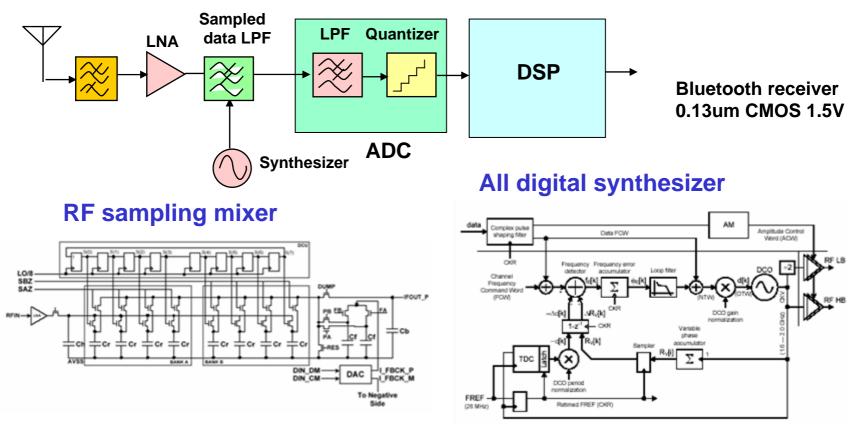

**Discrete-time Bluetooth** 0.13um, 1.5V, 2.4GHz

jure 15.1.7: Die micrograph of the single-chip Bluetooth transceiver.

K. Muhammad (TI), et al., ISSCC2004, pp.268

31

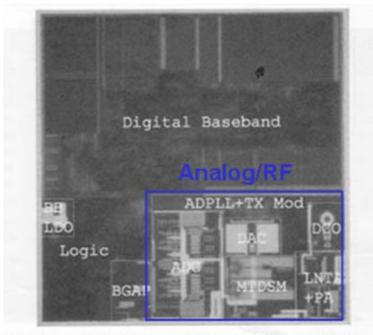

#### Digital oriented Wireless SoC architecture

Analog/RF circuits will continue to be needed, but many analog RF circuits will be replaced by digital like circuits.

#### Digital oriented architecture

K. Muhammad (TI), et al., ISSCC2004, pp.268

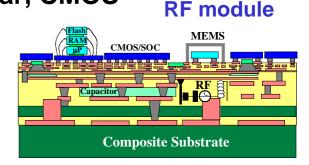

# Module and SiP technology for the future digital consumer electronic systems

#### Why module and SiP technology is important

- Higher integration in small space

- Cellular phone

- Memory module

- Heterogeneous devices integration

- Camera module: Lens + Imager + DSP + Flash+ (Power supply)

- Wireless module: Filter, LCR, GaAs, Bipolar, CMOS

- Easy to use

- Less adjustment points

- Less EMI issues

- High cost and time performance

- Optimum design rules; Analog + Digital

- Can use cheep standard products; DRAM, Flash

- High performance and low power

- SiS technology between CPU and DRAM

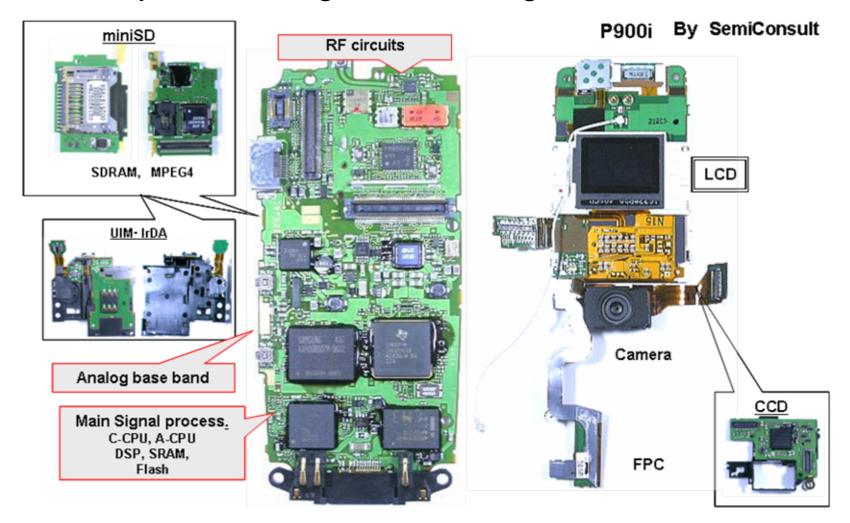

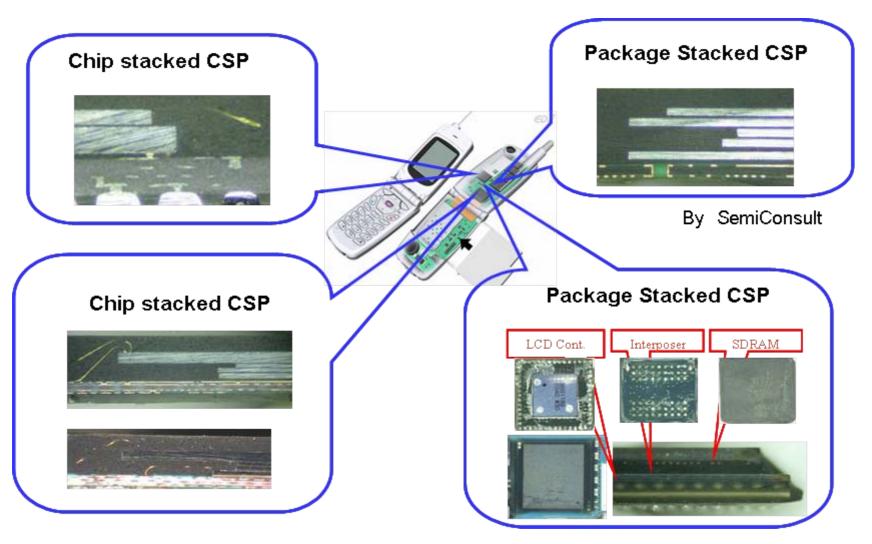

#### SiP for cellular phone

Many SiPs have been used in the cellular phone.

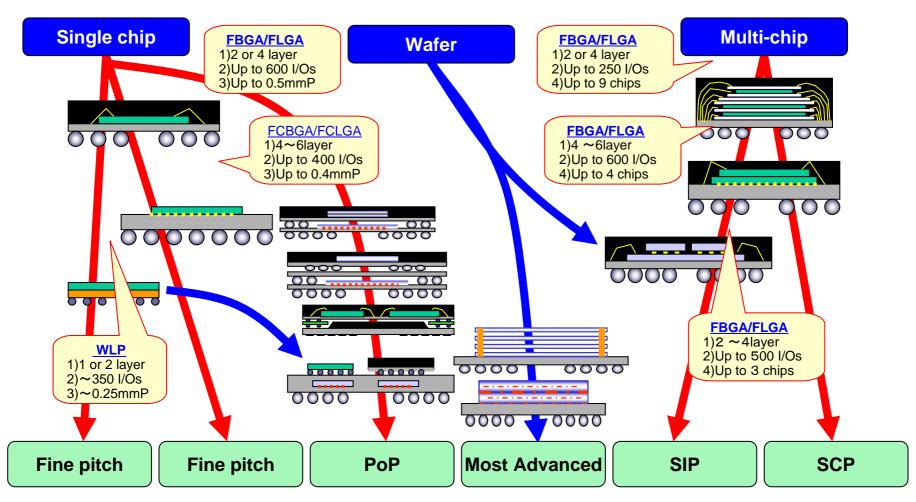

#### Direction of LSI Packages/Substrate

Remarks: 1) Necessary substrate layers, 2) Existing pin count, 3) Terminal pitch

By Semiconsult

36

#### 3D integration technology

3D integration can realize high electric performances equal to on-chip interconnection.

|                      | Conv. SiP               | TCV              |  |  |

|----------------------|-------------------------|------------------|--|--|

| Figure               |                         |                  |  |  |

| Interconnect method  | Wire bond               | Bamp + Inner bia |  |  |

| Wire length          | Several mm~several 10mm | <100 µm          |  |  |

| Inductance           | 10 nH                   | 19 pH            |  |  |

| Capacitance          | 8 pF                    | 0.1 pF           |  |  |

| Minimum package size | > Chip size+5 mm        | Chip size        |  |  |

| Thickness (4 chip)   | 490 µm                  | 240 μm           |  |  |

37

# System in Silicon technology

Dedicated DRAM with 1024 (512 x 2) parallel connections realizes 19GB/s data transfer, which is higher than DDR3 (13GB/s).

- Block-base SoC design and multi-chip fabrication

- The system is encapsulated by Silicon (→SiS)

- Global routing over different substrates using SiIP

Micro-bumps for the high density connection

|                                                                                    |                             | Bus width      | NG (~32bit)             | OK          |  |  |

|------------------------------------------------------------------------------------|-----------------------------|----------------|-------------------------|-------------|--|--|

| Memory Capacity (Mbit)                                                             |                             | Capacity       | OK(16M~1G)              | NG(~64M)    |  |  |

|                                                                                    |                             | Power          | NG                      | OK          |  |  |

| 512                                                                                |                             | TTM / TTV      | OK                      | NG          |  |  |

| 312                                                                                |                             | Cost (NRE)     | OK                      | NG          |  |  |

| 256                                                                                |                             | ASIC pin-count | NG (Bonding limit)      | OK          |  |  |

| 200                                                                                | SIP with SiS                |                | — CITD (CIT)            | ,           |  |  |

| 128                                                                                | SIP with generic Micro Bump |                | SiIP (Silicon Int       | erposer)    |  |  |

|                                                                                    | DRAM                        |                |                         |             |  |  |

| 64                                                                                 |                             | 1              | / Global / Power supply | y / Clock   |  |  |

|                                                                                    |                             | 0,             | Global / Fower supply   | y y Clock   |  |  |

| 32                                                                                 | eDRAM SoC                   |                |                         |             |  |  |

|                                                                                    | EDINAM SOC                  |                |                         |             |  |  |

| 16 l                                                                               | 10 00 04 100 050 510 Local  |                |                         | <del></del> |  |  |

| 16 32 64 128 256 512 Local Memory Bus width (bit) ~ Band width  SiS-DRAM  SiS-DRAM |                             |                |                         |             |  |  |

| rientory bus width (bit) ~ band width                                              |                             |                |                         |             |  |  |

SIP with generic

**eDRAM**

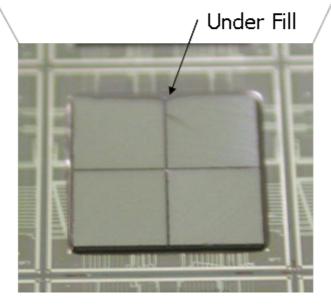

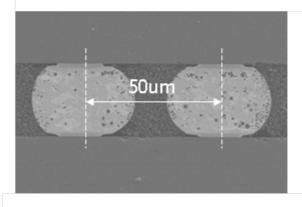

# System in Silicon technology

#### SiS with SiIP wafer

(Bump: 40um / 50um pitch)

a partial cross section for 50um pitch

Pictures are provided by

# **Development management**

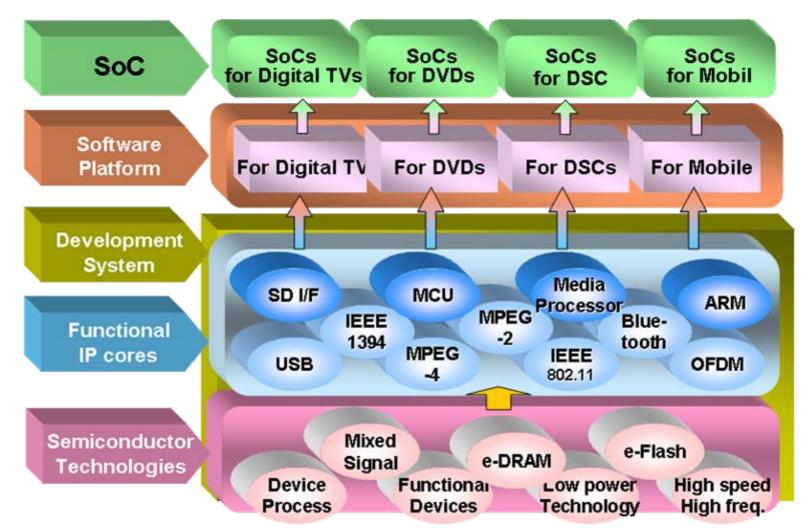

#### Technology platform of SoC for digital CE

SoC for digital CE needs a technological platform from device/circuits to software.

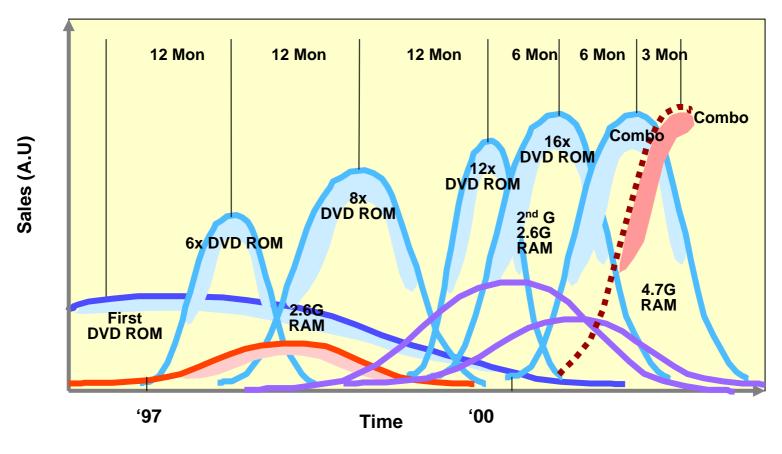

#### Reduction of development TAT

Unfortunately, production cycle time of digital CE becomes shorter. Short development TAT and tangible development are vital.

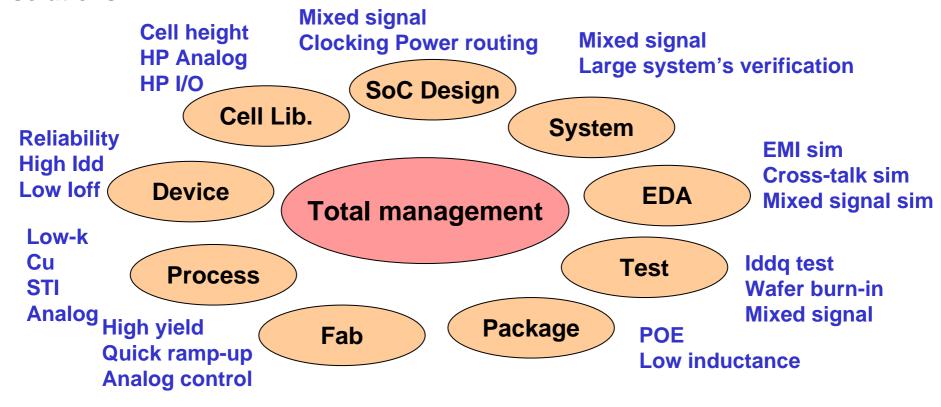

#### Total management for SoC development

The SoC development needs a total management system for the optimization over several technology areas. DFM becomes crucial.

Making the roadmap must be effective to find future demands, issues, and solutions

Roadmap: Future demands, issues, and solutions

# **Summary**

- The digital consumer systems need the high throughput and low power processing capability and mixed signal interfaces, however the cost should be suppressed.

- The progress of LSI technology has realized it as System on a Chip (SoC). The use of application oriented architecture has attained the targets.

- However, the next generation SoC for the digital CE should use the software conscious unified architecture to address the issue of the software development limitation and the multimedia convergence.

- The SiP is essentially needed for not only the realization of high density systems but also the realization of high cost-performance systems.

- Furthermore, SiP (SiS) has a great potential to solve the essential memory bottleneck which limits the processing throughput and to solve the noise and power issues.

- Developing technology platform and total management systems for SoC development are vital for the business success.