# Driving the SoC development for digital consumer electronics

Akira Matsuzawa

#### Tokyo Institute of Technology (Matsushita Electric Ind., Co. before this April)

Estimedia A. Matsuzawa

### Contents

- Digital consumer electronics and SoC

- Architecture design

- Mixed signal technology

- Global development management

# **Digital consumer electronics and SoC**

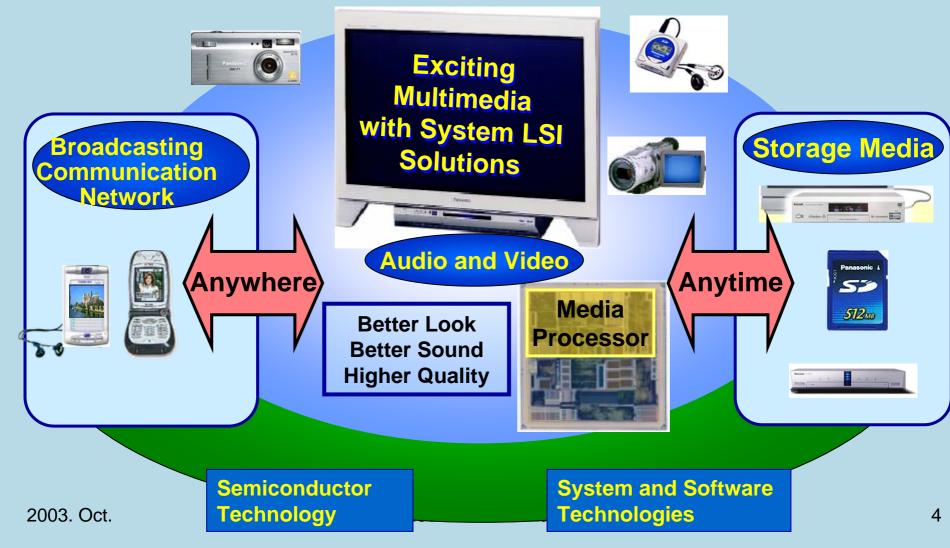

#### **Exciting Multimedia world with SoC!**

The new consumer electronics era has been emerged. The key technologies are digital multimedia and System on a Chip.

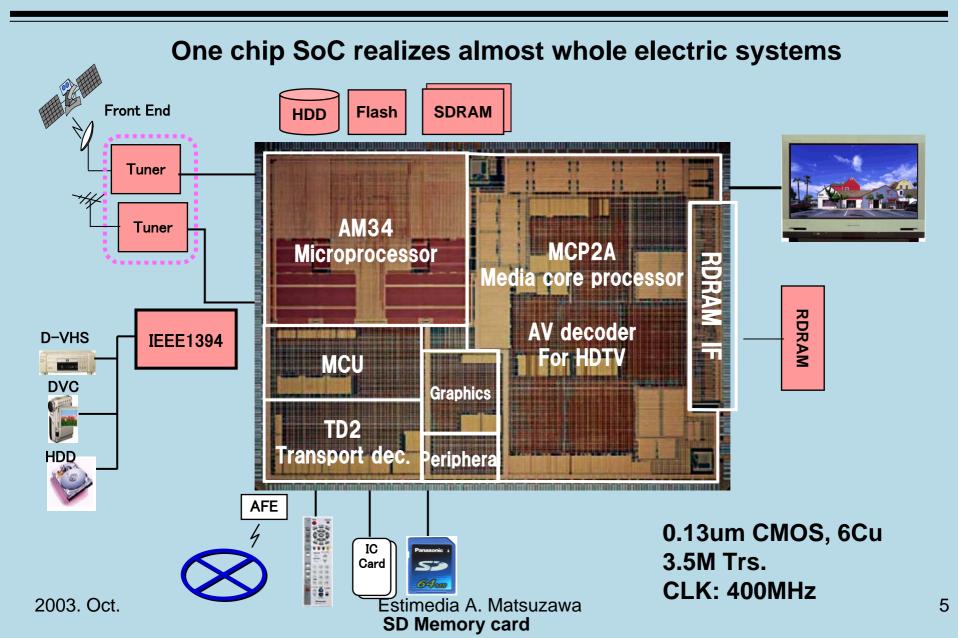

#### System configuration of Digital high-definition TV

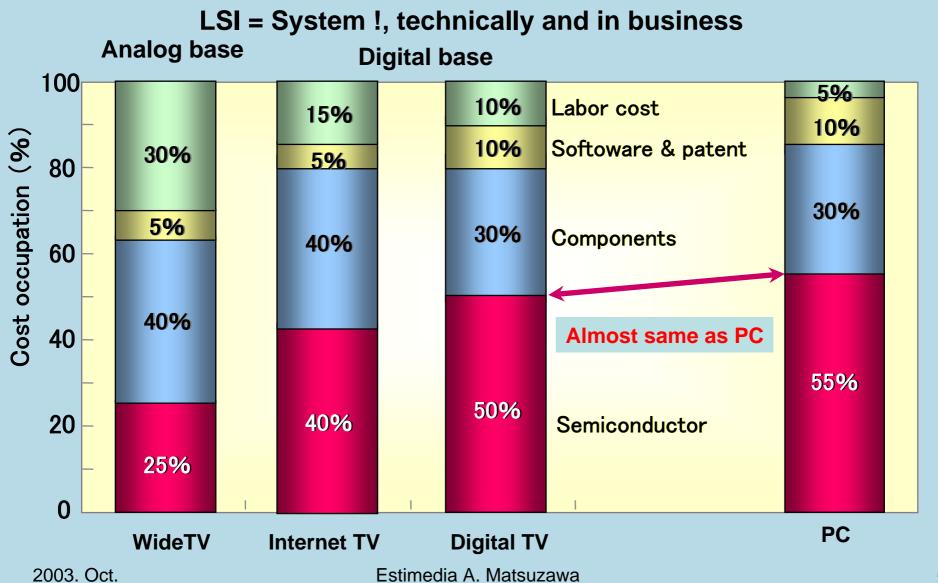

#### Impact of digital tech. on consumer business

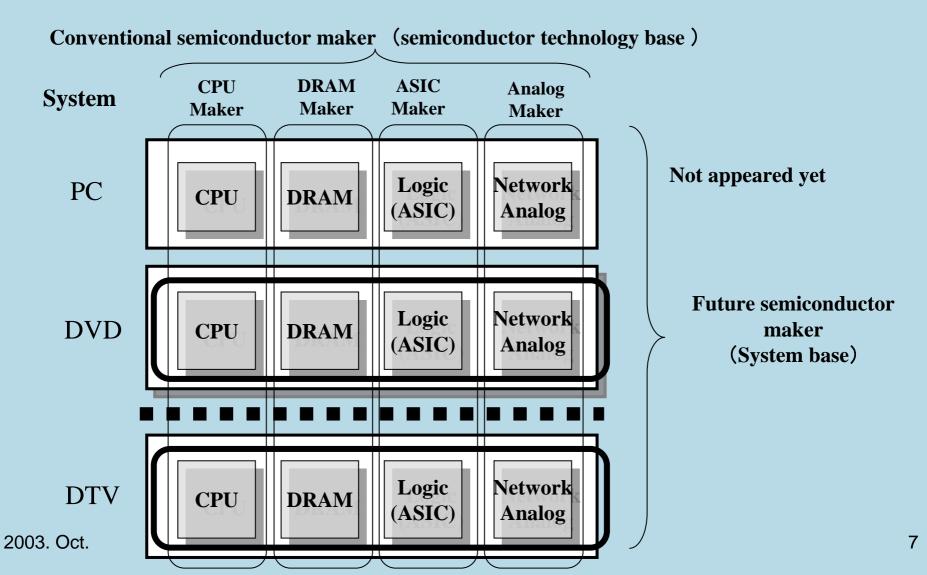

# New semiconductor business scheme

SoC will reform the semiconductor business scheme from vertical to horizontal.

# Architecture design

## **Architecture design**

#### The architecture optimization based on a system analysis is a key.

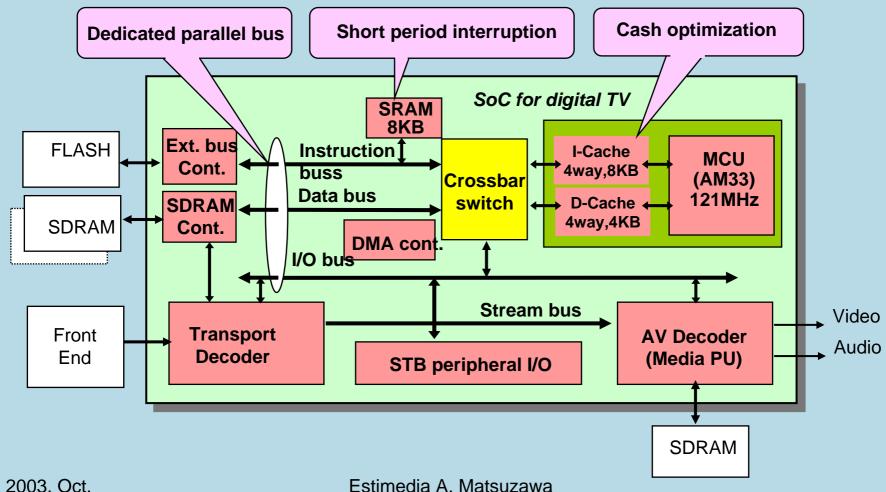

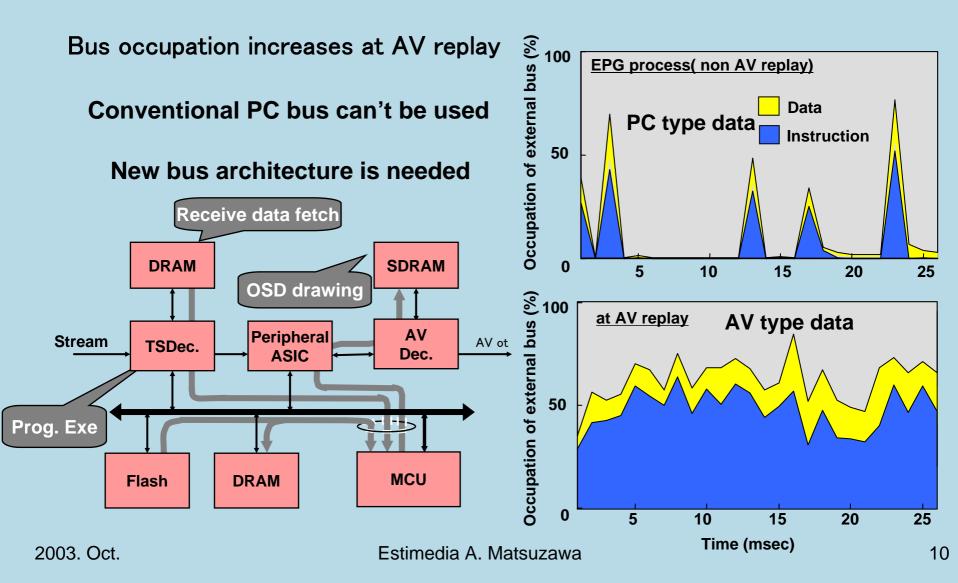

## System analysis 1: External bus

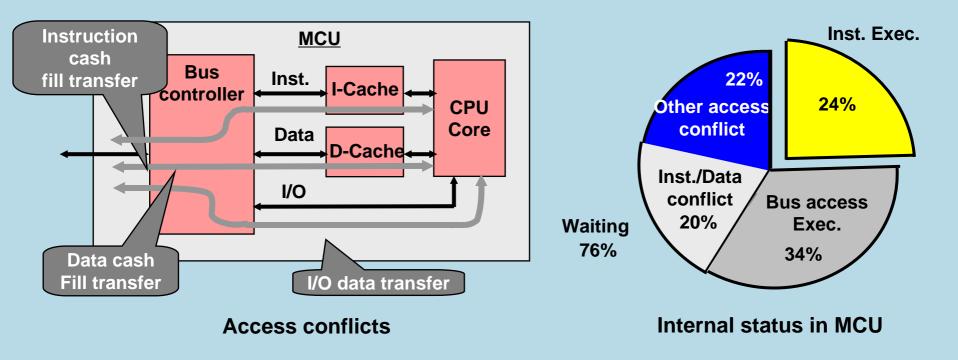

# System analysis 2: Internal bus

#### Instruction execution is only 1/4

#### Many conflicts between data and instructions

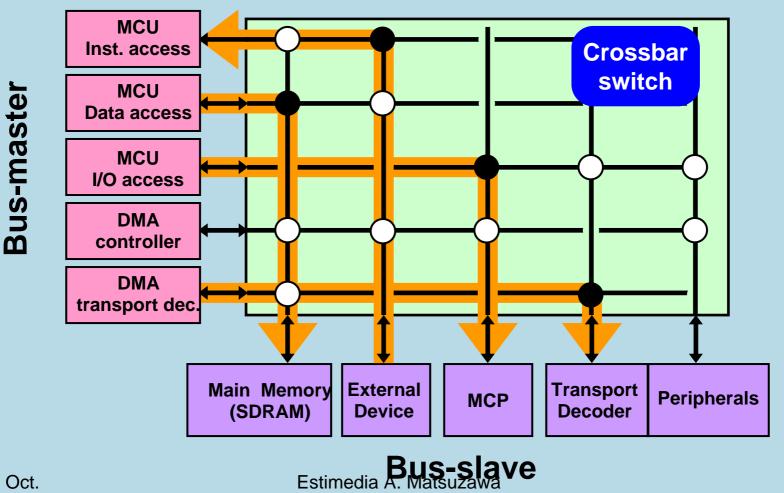

### **Solution: Crossbar switch**

Bus-master can access to bus slave in each, independently

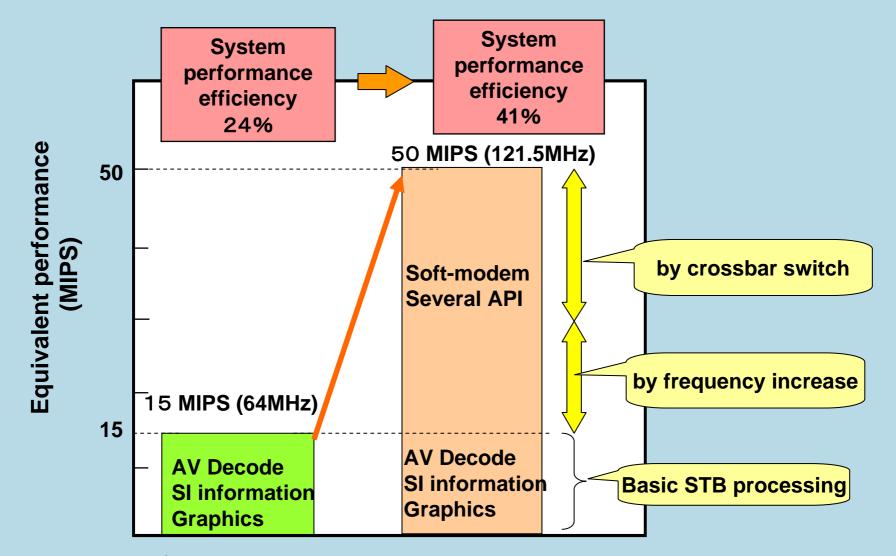

### **Performance improvement**

2003. Oct.

Conventional Estimesoc forsdigital TV

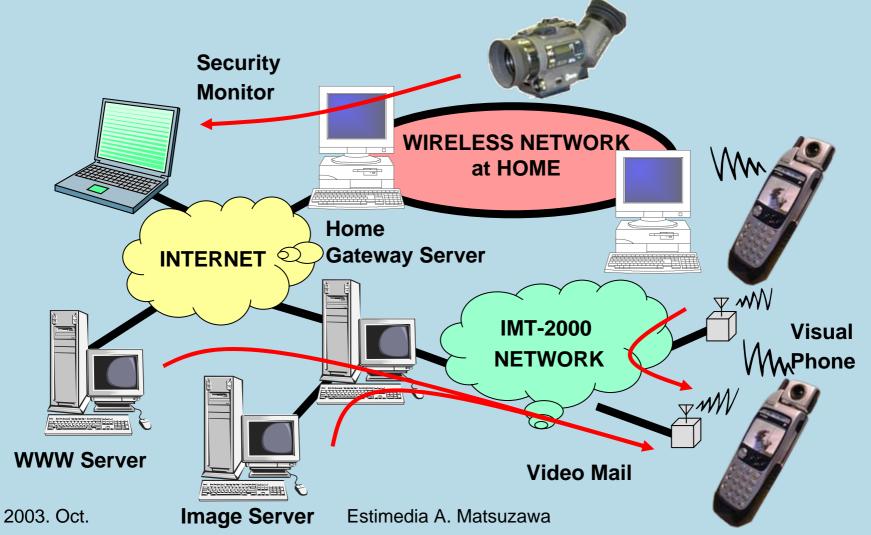

# **MPEG4 World**

The MPEG4 technology are going to be used not only for a cellular phone, but also for internet and consumer electronics

### **MPEG4 Codec and decoder**

#### **MPEG4** Codec

0.18um e-DRAM 31M Tr 90 mW@54MHz

15fps (Core@L1 decode) 30 fps (Simple@L3 decode)

#### **MPEG4** Decoder

0.18um CMOS 11M Tr 11 mW@27/54MHz

15fps (Core@L1 decode)

15

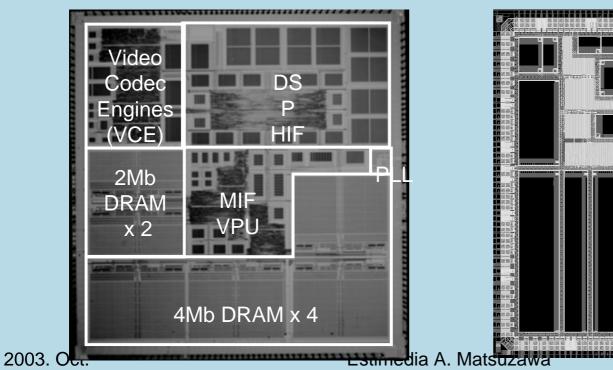

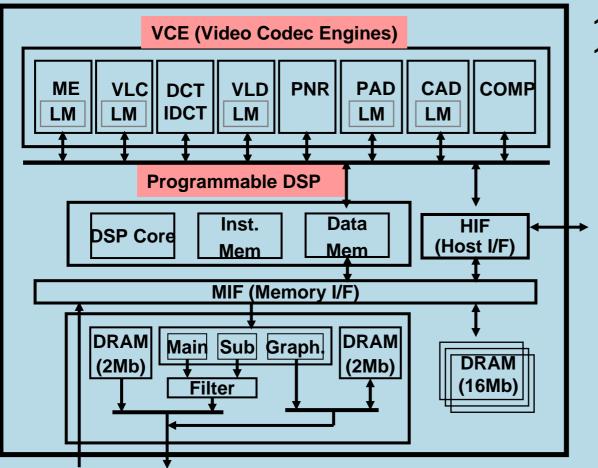

# **MPEG4** Codec

DSP with Vector Pipeline and dedicated HW engines enables high throughput and low power video processing

Video Output

2003. Oct.

1.5 GOPS: Simple@L1 12 GOPS: Simple@L3 6 GOPS: Core@L1

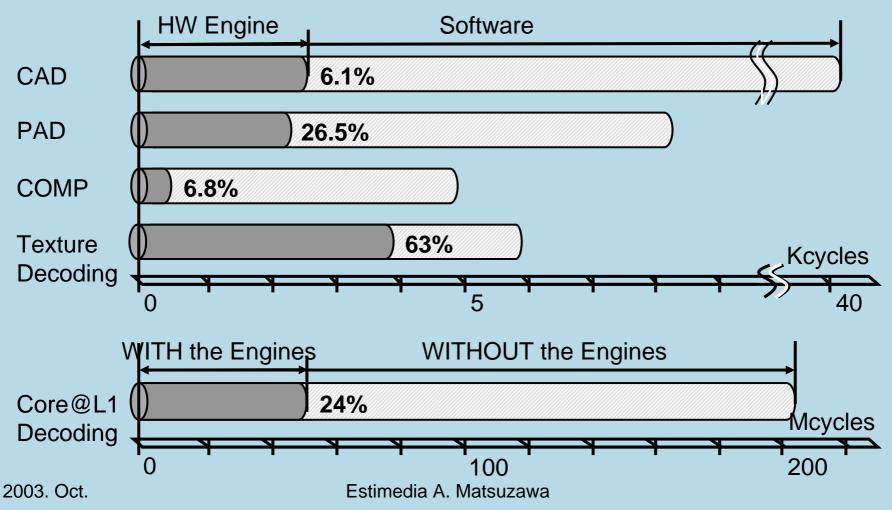

# **Performance of core decoding**

Hardware engines increase the performance 4 times higher

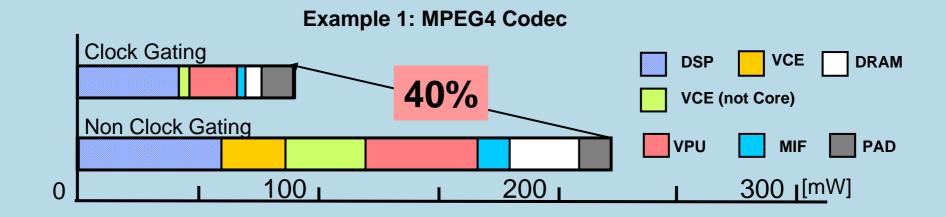

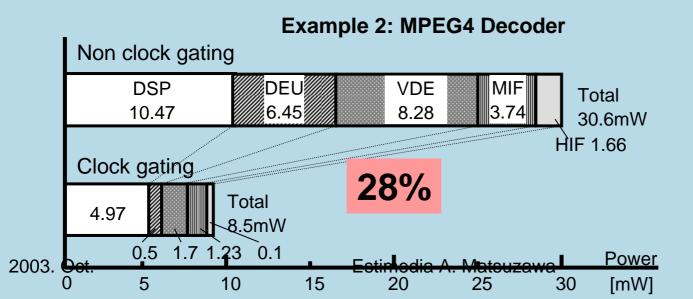

# **Clock gating**

The sophisticated clock gating is very effective to reduce the power consumption.

18

# **Mixed signal technology**

# Mixed signal technology

The mixed signal is vital to current SoC for the consumer and networking. However, conventional analog needs 2 or 3 redesigns! How to develop it without re-design!

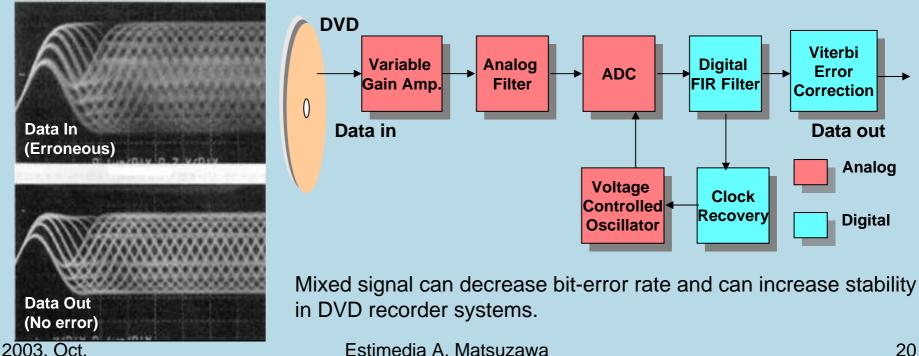

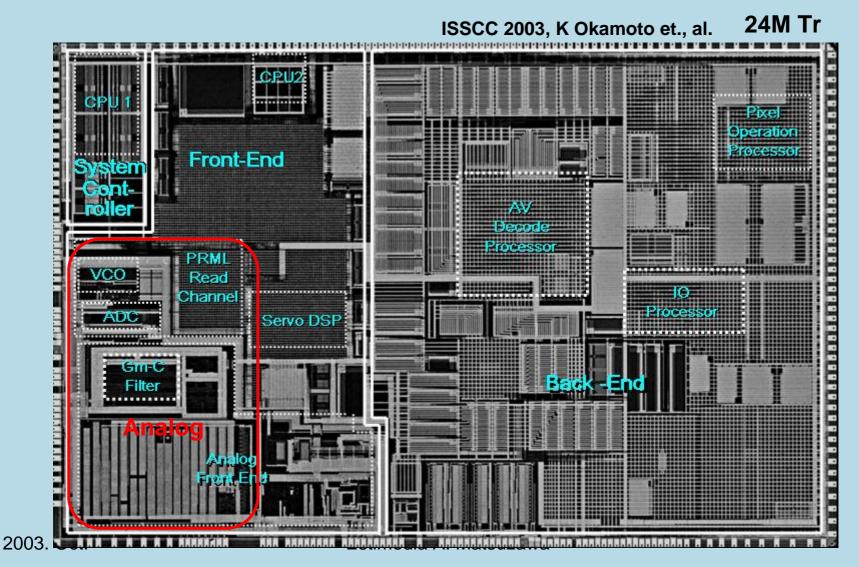

# Mixed signal SoC for DVD systems

The SoC integrates analog FE, font-end, and back-end in 0.13um tech.

# Strategy for the mixed signal SoC

- System design

- **Digital calibration** for analog adjustment and unknown parameters.

- System optimization to reduce analog area and increase robustness.

- System verification

- Fast and accurate mixed signal system simulator with behavioral model to verify and optimize the mixed signal system.

- Create the **target performance** for circuit blocks.

- Circuit design

- Ultra fast and accurate circuit simulation for P.V.T and fluctuation analysis to verify the performance and robustness.

- Circuit optimizer to find the sweet spot of the circuit.

- Automated creation of analog behavioral model for system simulation.

- Process and device development

- Develop suitable analog option device

- Early **analog parameter extraction** (mismatch, temp. and voltage chara.)

- Monitor and control the analog parameters in Fab.

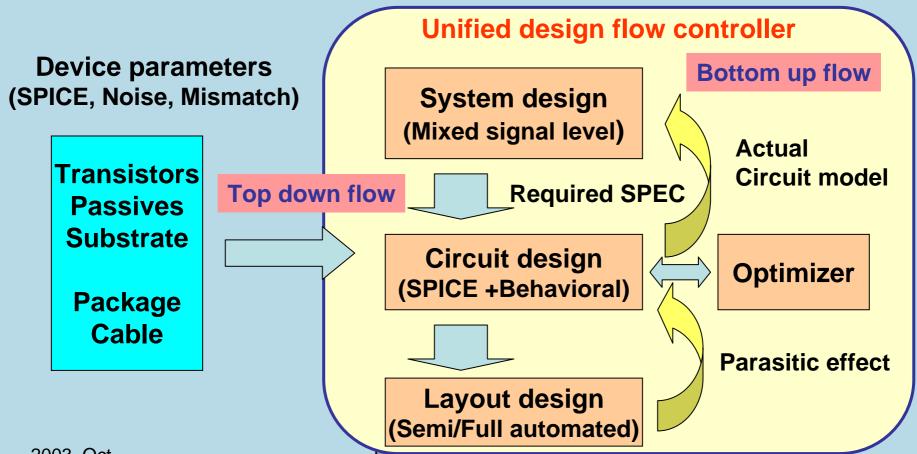

# Design flow for mixed signal SoC

The design flow from a system to a layout with top down and bottom up process should be used for designing the mixed signal SoC. The accurate and a variety of device parameters is an another key.

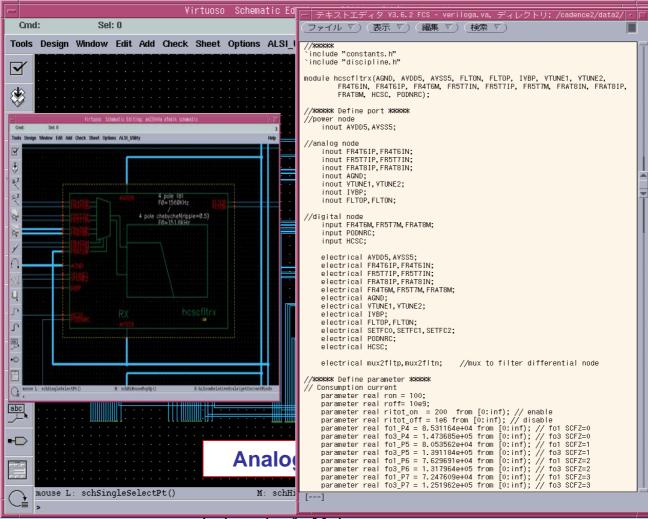

# Hierarchical and behavioral system design

#### This system should be described in behavioral language, hierarchically.

2003. Oct.

Estimedia A. Matsuzawa

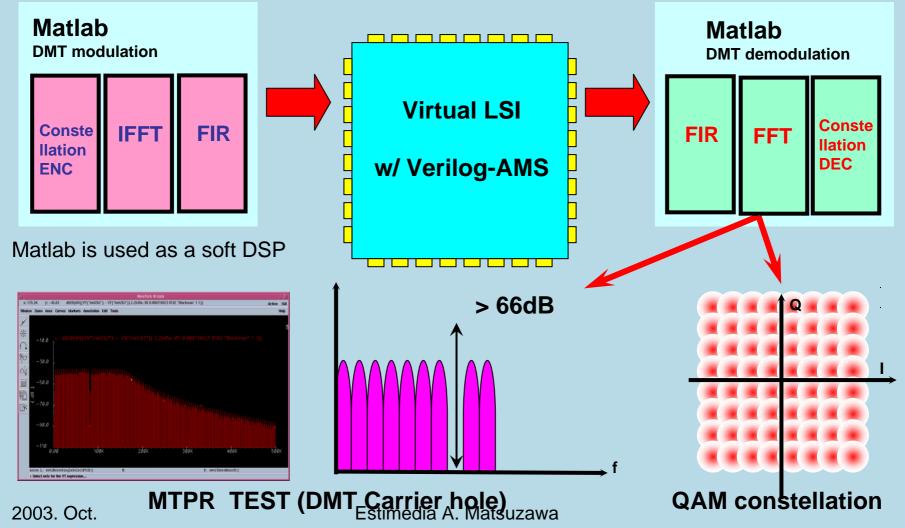

#### Virtual System test using verilog AMS and Matlab

# We can simulate the performance of mixed signal system, using Verilog AMS and Matlab.

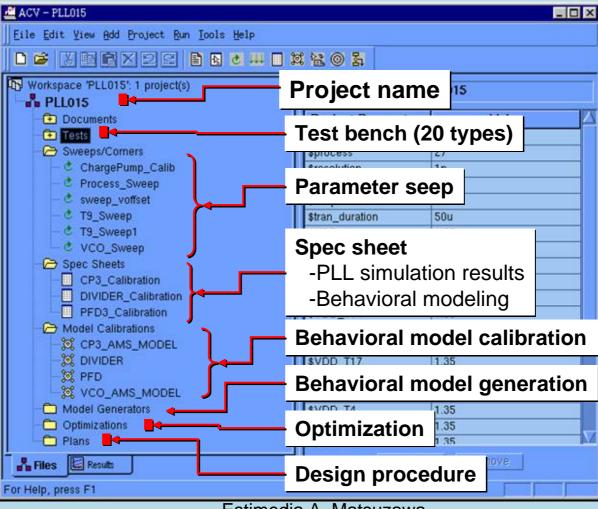

#### **Controller for automated simulation**

#### Simulation controller enables fast and automated simulation steps

# **Global development management**

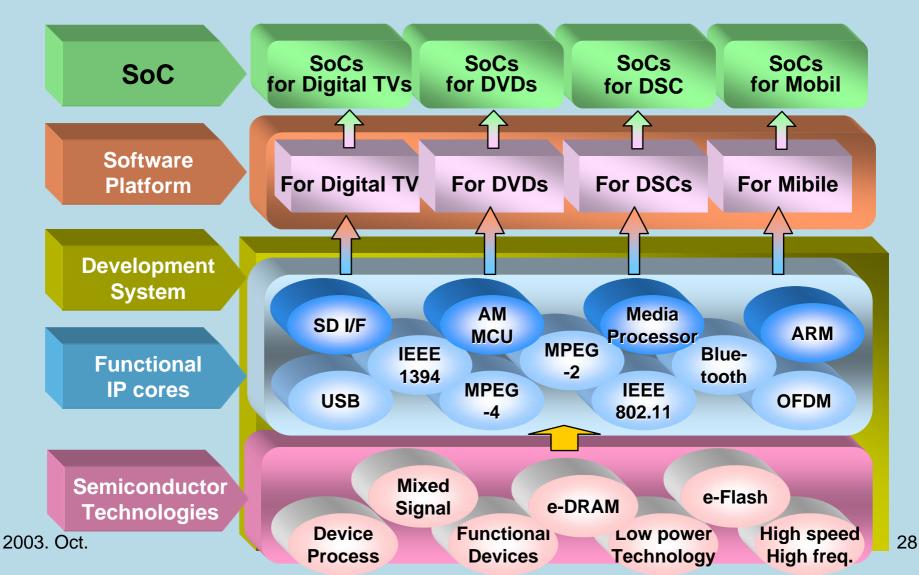

# **Development Platforms for SoC**

SoC needs several technology layers from system and software to device

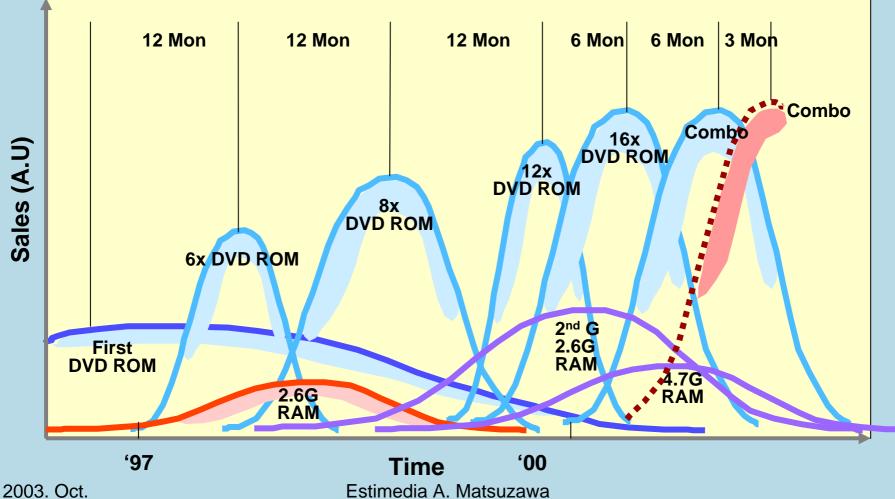

# Narrow development time slot

The development time slot is very narrow. So "Just in time" develop is required.

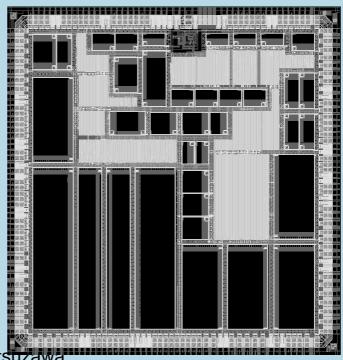

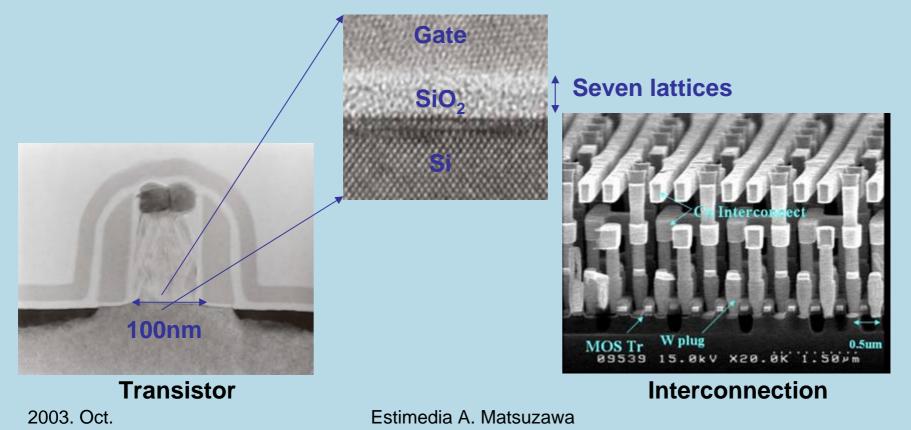

# **Scaled CMOS**

Current Scaled Si technology is very artistic.

How to control it and how to increase the production yield quickly!

Matsushita's 0.13um CMOS

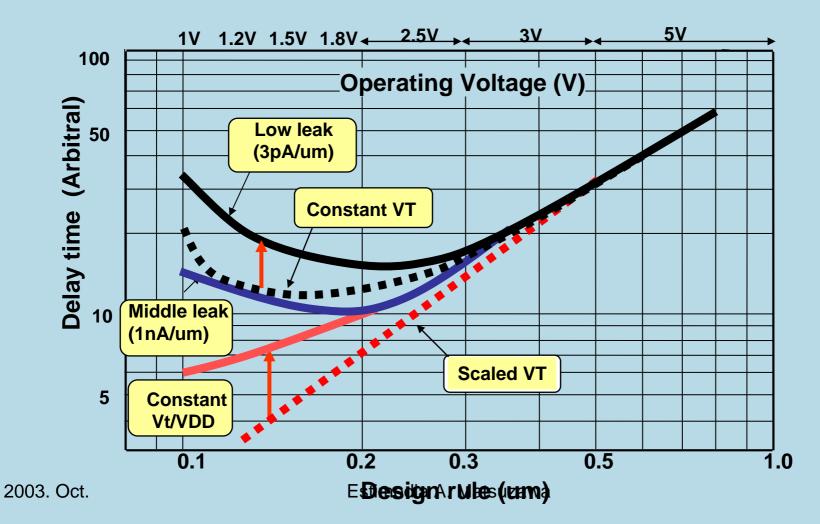

# **Choice of transistor**

A variety of transistors has increased.

Choose the proper transistor depending on the systems

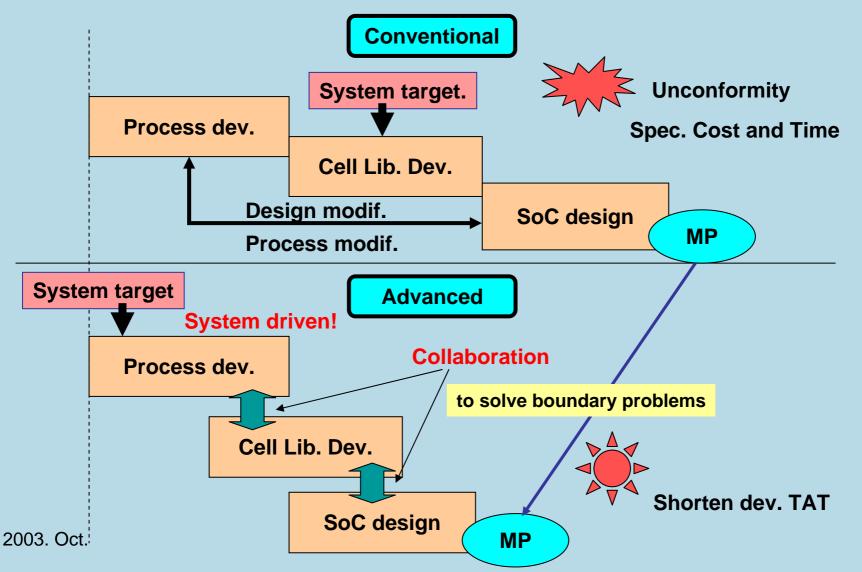

# System target driven development

#### System target driven can reduce unconformities and shorten the TAT.

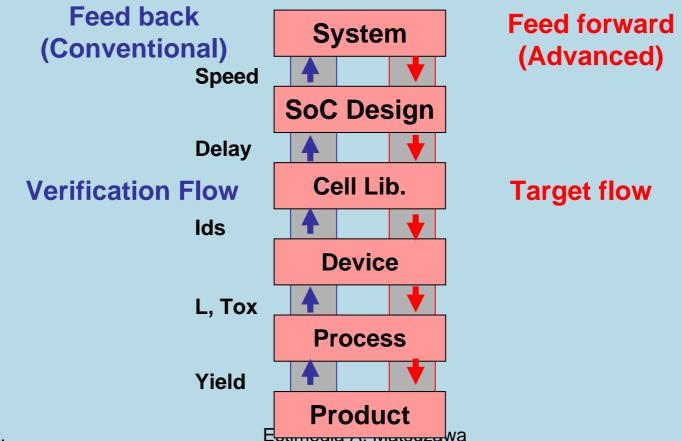

# **Bidirectional design flow**

Bidirectional design flow; feed forward flow, as well as feedback flow can pass early targets to different groups. This shorten the TAT and reduce the conflicts.

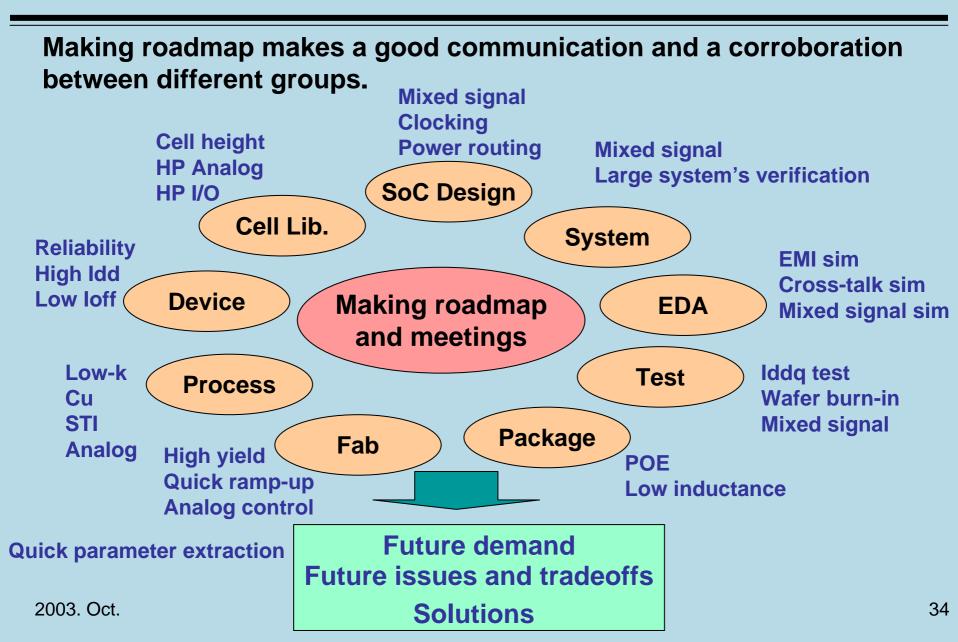

# Making roadmap

# Summary

- Digital consumer electronics based on multimedia technology has emerged and become big market.

- SoC also has become a dominant along with this technology.

- Architecture of SoC should be optimized for the application system.

- The mixed signal technology is vital for SoC. Increase the design quality and development speed.

- SoC development needs a variety of technology layers from a system to a device and needs several optimization for the applications.

- A global development managing system is an another key to success. Make collaboration and unification over different technology groups to shorten the development time and increase customer satisfaction.